# **ANALOG & DIGITAL ELECTRONICS**

## **M.Sc. PHYSICS**

## **SEMESTER-I, PAPER-IV**

## **LESSON WRITERS**

#### **Prof. Sandhya Cole**

Professor Department of Physics University College of Sciences Acharya Nagarjuna University

#### Prof. G. Naga Raju

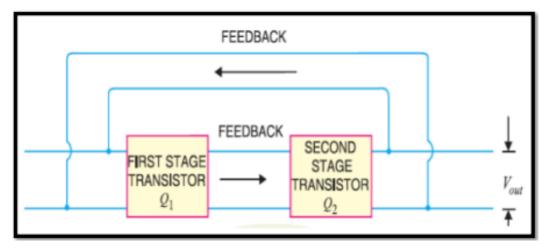

Professor Department of Physics University College of Sciences Acharya Nagarjuna University

## Prof. R.V.S.S.N. Ravi Kumar

Professor Department of Physics University College of Sciences Acharya Nagarjuna University

#### Prof. Ch. Linga Raju

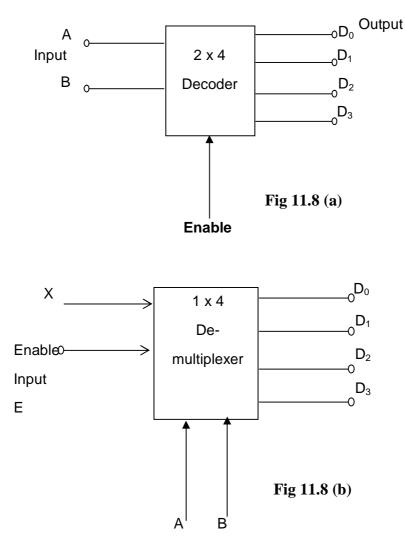

Professor Department of Physics University College of Sciences Acharya Nagarjuna University

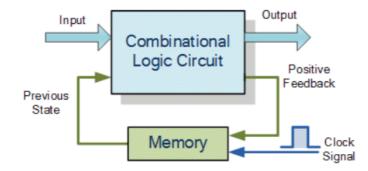

## **EDITOR**

#### **Prof. Sandhya Cole**

Professor Department of Physics University College of Sciences Acharya Nagarjuna University

## DIRECTOR, I/c

## **Prof. V. Venkateswarlu**

M.A., M.P.S., M.S.W., M.Phil., Ph.D.

Professor Centre for Distance Education Acharya Nagarjuna University Nagarjuna Nagar 522 510

Ph: 0863-2346222, 2346208 0863- 2346259 (Study Material) Website www.anucde.info E-mail: anucdedirector@gmail.com

## **M.Sc. PHYSICS: ANALOG & DIGITAL ELECTRONICS**

First Edition : 2025

No. of Copies :

© Acharya Nagarjuna University

This book is exclusively prepared for the use of students of M.Sc. Physics, Centre for Distance Education, Acharya Nagarjuna University and this book is meant for limited circulation only.

**Published by:**

**Prof. V. VENKATESWARLU** Director, I/c Centre for Distance Education, Acharya Nagarjuna University

**Printed at:**

## FOREWORD

Since its establishment in 1976, Acharya Nagarjuna University has been forging ahead in the path of progress and dynamism, offering a variety of courses and research contributions. I am extremely happy that by gaining 'A+' grade from the NAAC in the year 2024, Acharya Nagarjuna University is offering educational opportunities at the UG, PG levels apart from research degrees to students from over 221 affiliated colleges spread over the two districts of Guntur and Prakasam.

The University has also started the Centre for Distance Education in 2003-04 with the aim of taking higher education to the door step of all the sectors of the society. The centre will be a great help to those who cannot join in colleges, those who cannot afford the exorbitant fees as regular students, and even to housewives desirous of pursuing higher studies. Acharya Nagarjuna University has started offering B.Sc., B.A., B.B.A., and B.Com courses at the Degree level and M.A., M.Com., M.Sc., M.B.A., and L.L.M., courses at the PG level from the academic year 2003-2004 onwards.

To facilitate easier understanding by students studying through the distance mode, these self-instruction materials have been prepared by eminent and experienced teachers. The lessons have been drafted with great care and expertise in the stipulated time by these teachers. Constructive ideas and scholarly suggestions are welcome from students and teachers involved respectively. Such ideas will be incorporated for the greater efficacy of this distance mode of education. For clarification of doubts and feedback, weekly classes and contact classes will be arranged at the UG and PG levels respectively.

It is my aim that students getting higher education through the Centre for Distance Education should improve their qualification, have better employment opportunities and in turn be part of country's progress. It is my fond desire that in the years to come, the Centre for Distance Education will go from strength to strength in the form of new courses and by catering to larger number of people. My congratulations to all the Directors, Academic Coordinators, Editors and Lessonwriters of the Centre who have helped in these endeavors.

> Prof. K. Gangadhara Rao M.Tech., Ph.D., Vice-Chancellor I/c Acharya Nagarjuna University.

## M.SC. PHYSICS SYLLABUS SEMESTER - I, PAPER - IV 104PH24 - ANALOG & DIGITAL ELECTRONICS

#### **Course Objectives:**

- Introduction of Semiconductor Devices and the Opto-electronic devices and their analysis.

- Operational Amplifiers, Construction and working DC and AC analysis, Effect of Feedback.

- ✤ Acquiring the Knowledge in Communication Electronics and then the Digital electronics.

- ✤ Architecture of 8085 Microprocessor, Instruction set, Addressing modes and some illustrative programmes.

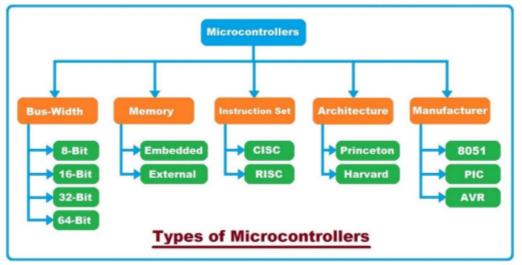

- ✤ Introduction to 8051 Microcontroller.

#### UNIT-I

#### **Semiconductor Devices**

Diodes, Junction diode, Tunnel diode, Photo diode, transistors, Silicon controlled rectifier, Uni junction transistor, Field effect transistor, JFET & MOSFET, CMOS, Opto-electronic devices: Solar cells, Photo detectors, LEDs.

#### **Learning Outcomes:**

- Construction and working of Tunnel diode, photodiode, Silicon Controlled Rectifier, Uni-junction Transistor.

- Know the Characteristics of FET, MOSFET and CMOS.

- Construction, working and applications of Solar Cells and LED's.

#### UNIT II

#### **Operational Amplifiers**

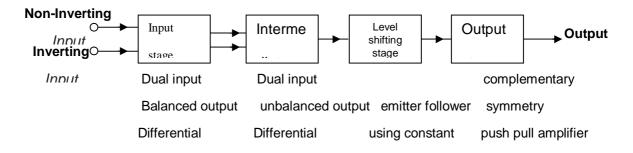

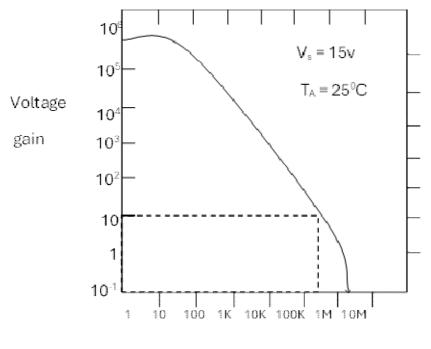

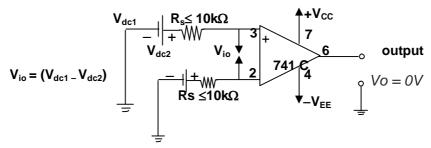

Differential Amplifier - Circuit Configurations - dual input, balanced output differential amplifier - DC analysis - Ac analysis, inverting and non-inverting inputs CMRR. Block diagram of a typical Op - Amp - analysis. Open loop configuration inverting and non - inverting amplifiers. Op-amp with negative feedback – voltage series feedback- effect of feedback on closed loop gain input resistance output resistance bandwidth and output offset voltage- voltage follower. Practical Op-amps

Input Offset Voltage- input bias current-input offset current, total output offset voltage, CMRR frequency response. Summing amplifier, Scaling and Averaging amplifiers, integrator and differentiator.

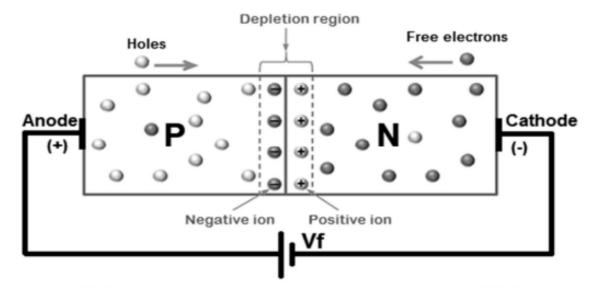

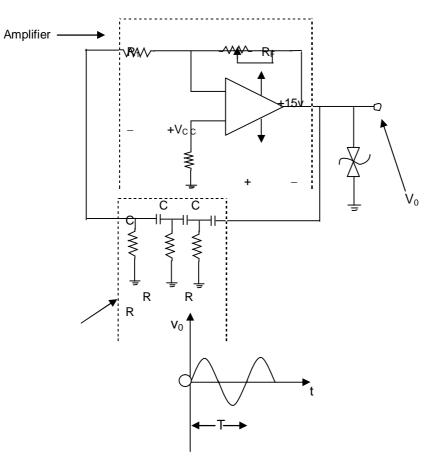

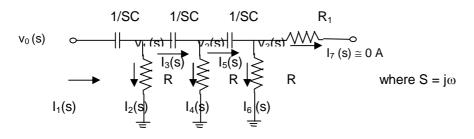

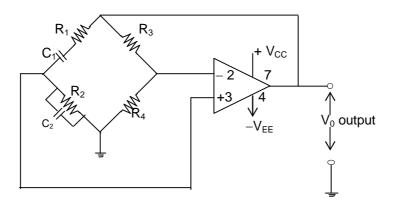

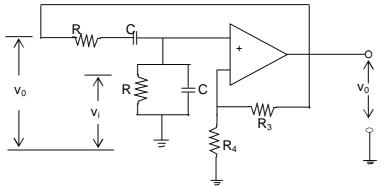

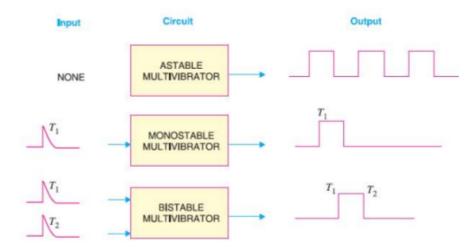

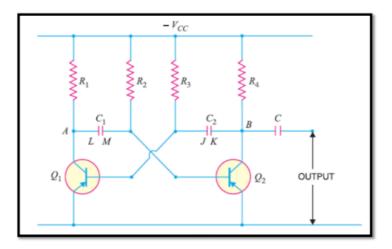

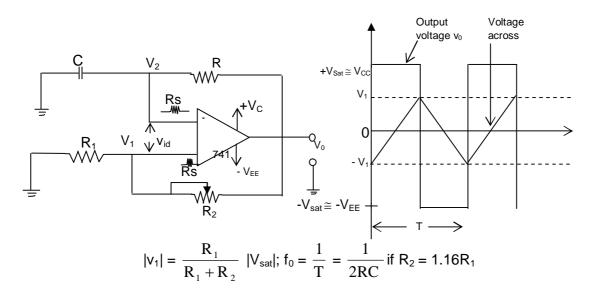

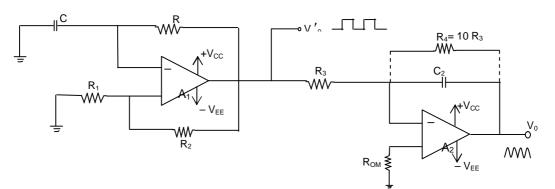

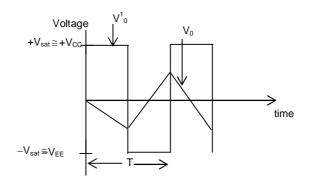

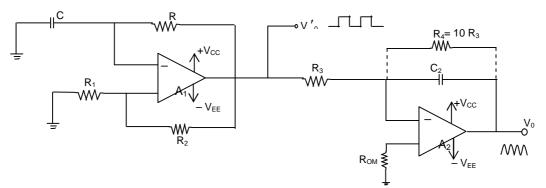

Oscillators Principles - oscillator types - frequency stability – response The phase shift oscillator, Weinbridge oscillator – Multi vibrators- Monostable and a stable-comparators-Square wave and triangular wave generators- voltage regulators.

### **Learning Outcomes:**

- To learn about the Differential amplifier and then the Operational amplifier, AC and DC analysis, Characteristics, Effect of Feedback.

- Oscillators Principles, Construction and working of different types of Oscillators. Clear picture of Multivibrators and then the Comparators using Operational amplifiers.

### UNIT III

### **Communication Electronics**

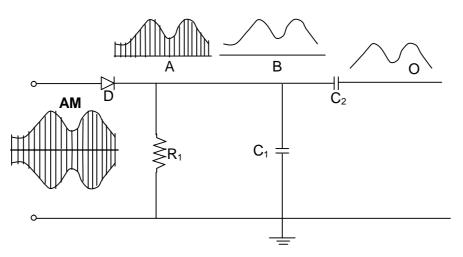

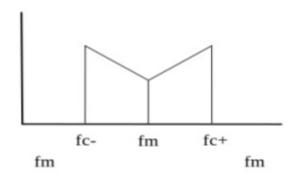

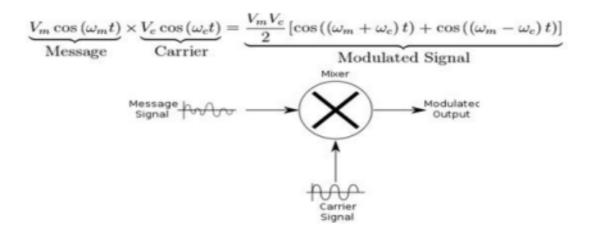

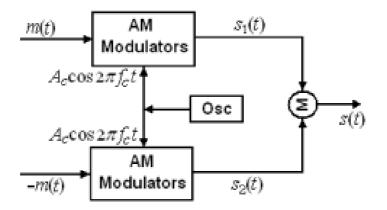

Amplitude modulation - Generation of AM waves - Demodulation of AM waves DSBSC modulation. Generation of DSBSC waves. Coherent detection of DSBSC waves, SSB modulation, Generation and detection of SSB waves. Vestigial side band modulation, Frequency Division Multiplexing (FDM).

### **Learning Outcomes:**

Acquiring knowledge in Communication electronics AM & FM, modulation and Demodulation.

### UNIT IV

### **Digital Electronics**

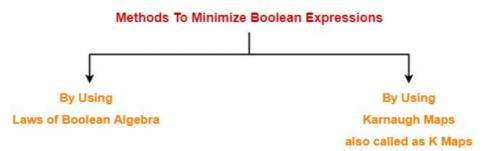

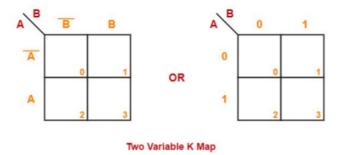

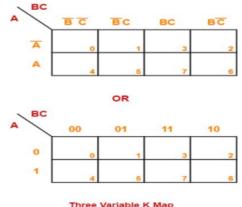

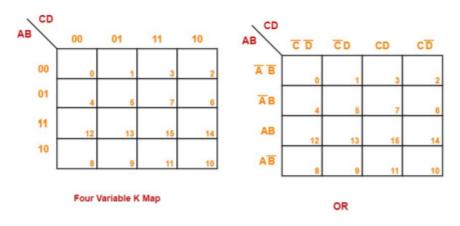

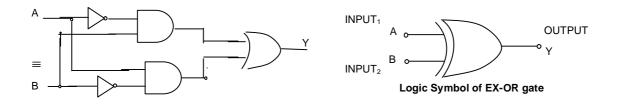

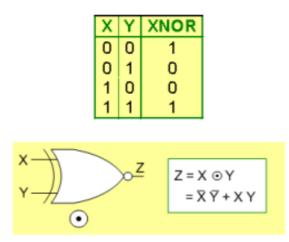

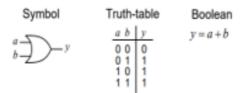

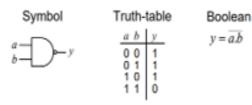

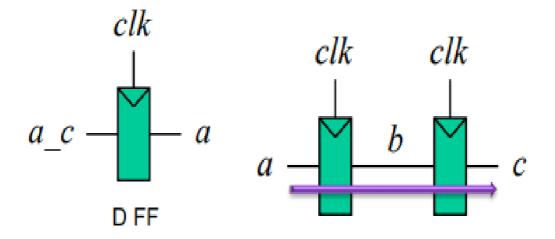

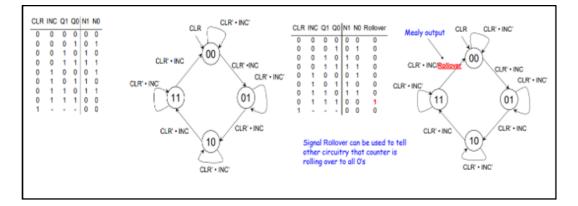

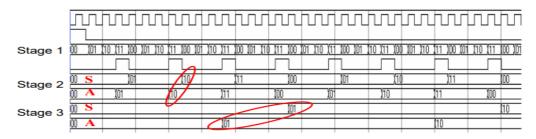

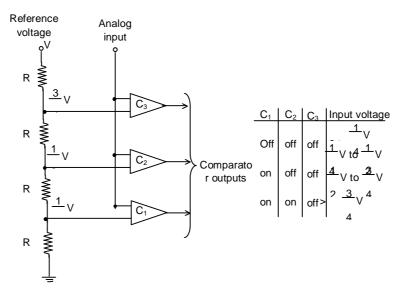

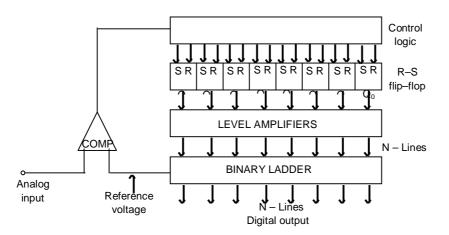

Simplification of Boolean Expressions: Algebraic Method, Karnaugh Method, EX - OR, EX - NOR Gates, Combinational Logic Gates - Decoder - encoders- Multiplexer (data selectors) - Application of Multiplexer - De multiplexer(data distributors), Sequential Logic - Flip-Flops: A 1- Bit Memory - The R-S Flip Flop, JK Flip-Flop - JK Master Slave Flip-Flop - T- Flip-Flop - D Flip-Flop - Shift Registers - Synchronous and Asynchronous Counters - Cascade Counters - A/D to D/A Converters.

#### **Learning Outcomes:**

- Expressing the Boolean expressions in a simple way, Karnaugh method.

- Learning the Combinational Logic Circuits, Multiplexer and Demultiplexer.

- Learning about the Sequential Logic circuits- Flip-Flops, Registers and Counters

## UNIT V

#### Microprocessors

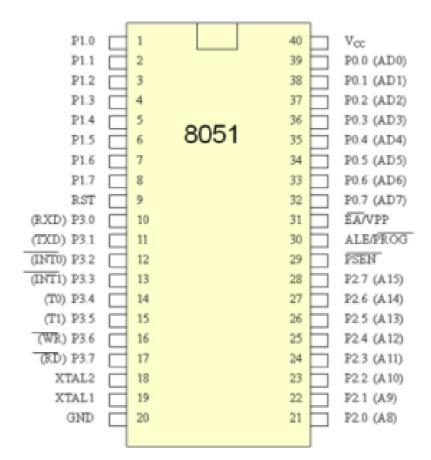

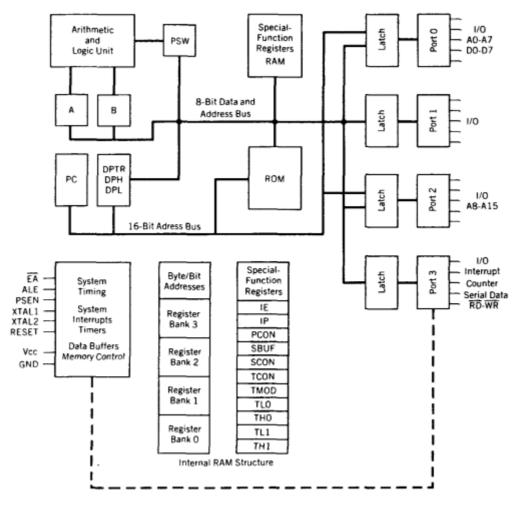

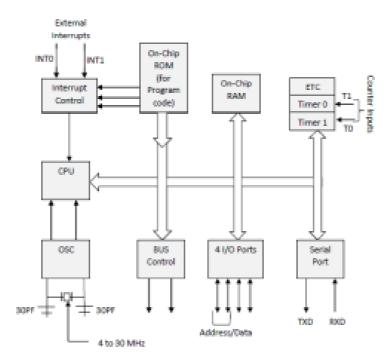

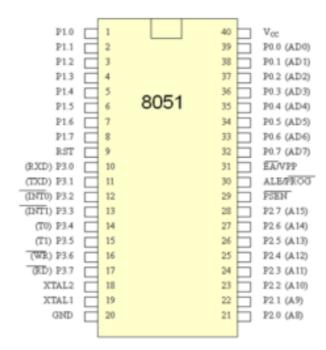

Introduction to microcomputers - memory - input/output - interfacing devices 8085 CPU - Architecture - BUS timings - Demultiplexing the address bus generating control signals - instruction set - addressing modes - illustrative programmes - writing assembly language programmes - looping, counting and indexing - counters and timing delays - stack and subroutine. Introduction to micro controllers - 8051 micro controllers - architecture & pin description.

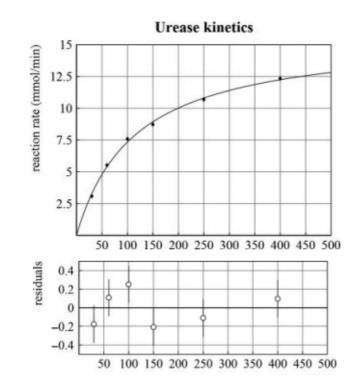

Data interpretation and analysis - Precision and accuracy - Error analysis, propagation of errors. Least squares fitting.

### Learning Outcomes:

- Knowledge about the Microprocessor and its Architecture

- Learning the Instruction Set, Addressing modes

- Writing the programmes using 8085 instructions

- Little knowledge about 8051 Microcontroller

#### **Course Outcomes:**

At the end of the course the student is expected to assimilate the following and possesses basic knowledge of the following.

- The design and functional performance of various semiconductor and optoelectronic devices such as Diodes, transistors, Solar Cells, Photo detectors and LEDs.

- To learn about the Differential amplifier and then the Operational amplifier, AC and DC Analysis, Characteristics, Effect of Feedback.

- Acquiring knowledge in Communication electronics AM &FM, modulation and Demodulation

- Learning the Combinational Logic Circuits, Multiplexer and Demultiplexer

- Learning about the Sequential Logic circuits- Flip-Flops, Registers and Counters

- Knowledge about the Microprocessor and its Architecture

#### **Text and Reference Books:**

- 1) Electronic Devices and Circuits G.K.Mithal (Khanna)

- 2) Integrated Electronics- Jacob Millman & C.C. Halkies (TMH)

- 3) Op-Amps & Linear Integrated Circuits Ramakanth A. Gayakwad

- 4) Op-Amps & Linear Integrated Circuits D. Mahesh Kumar (MacMillan)

- 5) Digital Principles and Applications by A.P.Malvino and Donald P.Leech TMH 1993.

- 6) Microprocessor Architecture, Programming and Applications with 8085/8086 by Ramesh S.Gaonkar, Wiely-Eastern 1987.

- 7) Digital Electronics: An Introduction to theory and Practical William. H.Gotnman.

## (104PH24) M.Sc. DEGREE EXAMINATION, MODEL QUESTION PAPER M.Sc. PHYSICS-FIRST SEMESTER ANALOG & DIGITAL ELECTRONICS

#### **Time: Three hours**

#### Maximum: 70 marks

#### **Answer ALL Questions**

#### **All Questions Carry Equal Marks**

- 1 a) Explain the working principle and applications of a silicon-controlled rectifier (SCR).

- b) Compare the construction and characteristics of JFET and MOSFET.

#### OR

- c) Describe the instruction set classification of the 8085 microprocessors.

- d) Write an 8085-assembly language program to perform multiplication of two numbers.

- 2 a) Explain the DC and AC analysis of a differential amplifier.

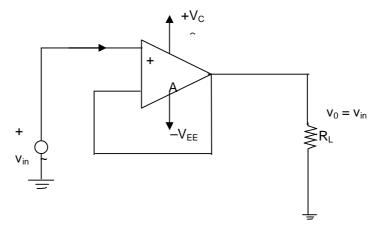

- b) What is the voltage follower configuration of an operational amplifier? Discuss its applications.

#### OR

- c) Describe the working and frequency stability of a phase shift oscillator.

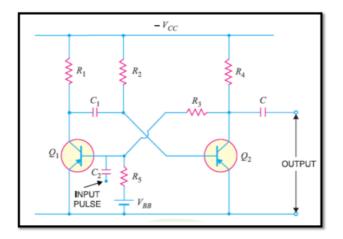

- d) Compare monostable and Astable multivibrators, with circuit diagrams.

- 3 a) What is amplitude modulation (AM)? Explain its advantages and disadvantages.

- b) Describe the working of coherent detection of DSBSC waves.

#### OR

- c) Compare frequency division multiplexing (FDM) and time division multiplexing (TDM).

- d) Explain the process of generation and detection of SSB waves.

- 4 a) What is the Karnaugh map method for simplifying Boolean expressions?

- b) Explain the working of a JK master-slave flip-flop with a neat diagram.

#### OR

- c) What is the function of a decoder and encoder in digital circuits?

- d) Compare synchronous and asynchronous counters with examples.

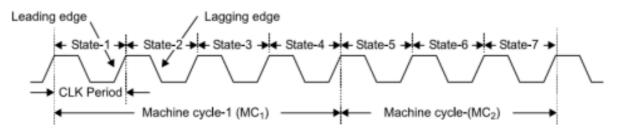

- 5 a) Explain the bus architecture and timing diagrams of the 8085 microprocessors.

- b) Describe the stack and subroutine operations in the 8085 microprocessors.

#### OR

- c) What are the key differences between the 8085 microprocessor and 8051 microcontrollers

- d) Explain the importance of error analysis and least squares fitting in data interpretation.

## CONTENTS

| S.No. | TITLE                                                                          | PAGE No.   |

|-------|--------------------------------------------------------------------------------|------------|

| 1     | ADVANCEMENTS IN SEMICONDUCTOR TECHNOLOGY:<br>DIODES, TRANSISTORSAND RECTIFIERS | 1.1-1.11   |

| 2     | EVOLUTION AND ADVANCEMENTS IN SEMICONDUCTOR<br>DEVICES                         | 2.1-2.14   |

| 3     | OPTO ELECTRONIC DEVICES                                                        | 3.1-3.10   |

| 4     | OPERATIONAL AMPLIFIERS                                                         | 4.1-4.16   |

| 5     | AMPLIFIERS AND FEEDBACK                                                        | 5.1-5.10   |

| 6     | PRACTICAL OP-AMPS                                                              | 6.1-6.10   |

| 7     | OSCILLATORS, MULTIVIBRATORSAND WAVEFORM<br>GENERATORS                          | 7.1-7.20   |

| 8     | MODULATION AND DEMODULATION                                                    | 8.1-8.16   |

| 9     | SSB MODULATION, VSB MODULATION AND FDM                                         | 9.1-9.9    |

| 10    | BOOLEAN ALGEBRA, LOGIC GATES AND KARNAUGH<br>MAPS                              | 10.1-10.11 |

| 11    | DECODERS, ENCODERS AND MULTIPLEXERS                                            | 11.1-11.9  |

| 12    | FLIP-FLOPS                                                                     | 12.1-12.9  |

| 13    | SHIFT REGISTERS, COUNTERS, AND A/D AND D/A<br>CONVERTERS                       | 13.1-13.17 |

| 14    | MICROCOMPUTERS AND 8085 MICROPROCESSORS                                        | 14.1-14.24 |

| 15    | MICROCONTROLLERS                                                               | 15.1-15.32 |

| 16    | DATA INTERPRETATION AND ANALYSIS                                               | 16.1-16.10 |

## **LESSON-1**

## ADVANCEMENTS IN SEMICONDUCTOR TECHNOLOGY: DIODES, TRANSISTORSAND RECTIFIERS

#### **1.0 AIM AND OBJECTIVES:**

The aim of this study is to explore the construction, characteristics, and applications of semiconductor devices such as diodes, transistors, and silicon-controlled rectifiers. It focuses on understanding the working principles of p-n junction diodes, tunnel diodes, and photodiodes, analyzing their current-voltage characteristics, and examining their role in rectification, amplification, and switching applications. The study also investigates the impact of doping on the depletion region, the function of transistors in electronic circuits, and the significance of semiconductor materials like silicon and germanium. Additionally, it covers the working of silicon-controlled rectifiers in power control applications and the tunneling effect in tunnel diodes. This knowledge is essential for understanding modern electronic components and their practical applications in various fields.

#### **STRUCTURE:**

- 1.1 Diodes

- **1.2** Junction Diode

- **1.3** Tunnel Diode

- 1.4 Photo Diode

- 1.5 Transistors

- 1.6 Silicon Controlled Rectifier

- 1.7 Summary

- **1.8** Technical Terms

- 1.9 Self-Assessment Questions

- 1.10 Suggested Readings

#### 1.1 DIODES:

A diode is a dispositive made of a semiconductor material, which has two terminals or electrodes (di-ode), that act like an on-off switch. When the diode is "on", it acts as a short circuit and passes all current. When it is "off", it behaves like an open circuit and passes no current. The two terminals are different and are marked as plus and minus in figure 1.1. If the polarity of the applied voltage matches that of the diode (forward bias), then the diode turns "on". When the applied voltage polarity is opposite (reverse bias), it turns "off". Of course this is the theoretical behaviour of an ideal diode, but it can be seen as a good approximation for a real diode.

| Centre for Distance Education 1.2 | Acharya Nagarjuna University |

|-----------------------------------|------------------------------|

|-----------------------------------|------------------------------|

A diode is simply a p-n junction (see 'Introduction into Semiconductor Physics') with the following characteristics:

- Under forward bias, it needs a small voltage to conduct. This voltage drop is maintained during conduction.

- The maximum forward current is limited by heat-dissipation ability of the diode. Usually it is around 1000 mA.

- There is a small reverse current

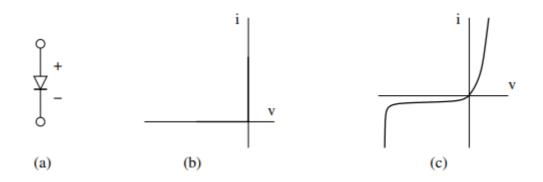

## Figure 1.1: (a) Diode symbol. (b) Current-voltage characteristics of an ideal diode. (c) IV curves for a real diode.

Every diode has a maximum reverse voltage (breakdown voltage) that cannot be exceeded without diode damage.

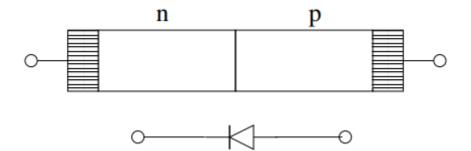

Figure 1.2: A p – n diode junction structure and the equivalent device schematics.

#### **1.2 JUNCTION DIODE:**

#### **1.2.1 Basic Operation:**

The diode is fabricated of a semiconductor material, usually silicon, which is doped with two impurities. One side is doped with a donor or n-type impurity which releases electrons into the semiconductor lattice. These electrons are not bound and are free to move about. Because there is no net charge in the donor impurity, the n-type semiconductor is electrically neutral.

The other side is doped with an acceptor or p-type impurity which imparts free holes into the lattice. A hole is the absence of an electron which acts as a positive charge. The p-type semiconductor is also electrically neutral because the acceptor material adds no net charge.

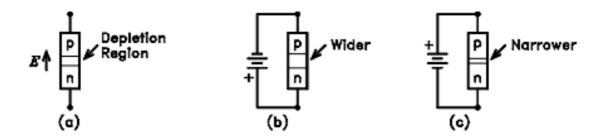

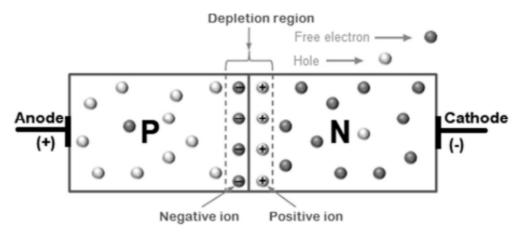

Figure 1.3 (a) illustrates the cross section of the diode. The junction is the dividing line between the n-type and p-type sides. Thermal energy causes the electrons and holes to move randomly. Electrons diffuse across the junction into the p-type side and holes diffuse across the junction into the n-type side. This causes a net positive charge to develop in the n-type side and a net negative charge to develop in the p-type side. These charges set up an electric field across the junction which is directed from the n-type side to the p-type side. The electric field opposes further diffusion of the electrons and holes. The region in which the electric field exists is called the depletion region. There are no free electrons or holes in this region because the electric field sweeps them out.

Figure 1.3: (a) Diode cross section. (b) Reverse biased diode. (c) Forward biased diode

Figure 1.3(b) shows the diode with a battery connected across it. The polarity of the battery is such that it reinforces the electric field across the junction causing the region to widen. The positive terminal pulls electrons in the n-type side away from the junction. The negative terminal pulls holes in the p-type side away from the junction. No current can flow. The diode is said to be reverse biased. Figure 1.3(c) shows the diode with the battery polarity reversed. The battery now tends to cancel out the electric field in the depletion region, causing its width to decrease. The positive terminal forces holes toward the junction. The negative terminal forces electrons toward the junction. A current flows which increases rapidly if the applied voltage is increased. The diode is said to be forward biased.

#### **1.3 TUNNEL DIODE:**

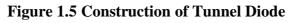

A Tunnel diode is a heavily doped p-n junction diode in which the electric current decreases as the voltage increases. In tunnel diode, electric current is caused by "Tunneling". The tunnel diode is used as a very fast switching device in computers. It is also used in highfrequency oscillators and amplifiers.

## **1.3.1 Symbol of Tunnel Diode:**

The circuit symbol of tunnel diode is shown in the below figure 1.4. In tunnel diode, the ptype semiconductor act as an anode and the n-type semiconductor act as a cathode.

**Figure 1.4 Symbol of Tunnel Diode**

The anode is a positively charged electrode which attracts electrons whereas cathode is a negatively charged electrode which emits electrons. In tunnel diode, n-type semiconductor emits or produces electrons, so it is referred to as the cathode. On the other hand, p-type semiconductors attract electrons emitted from the n-type semiconductor, so p-type semiconductor is referred to as the anode.

Leo Esaki observed that if a semiconductor diode is heavily doped with impurities, it will exhibit negative resistance. Negative resistance means the current across the tunnel diode decreases when the voltage increases. In 1973 Leo Esaki received the Nobel Prize in physics for discovering the electron tunneling effect used in these diodes.

A tunnel diode is also known as Esaki diode which is named after Leo Esaki for his work on the tunneling effect. The operation of tunnel diode depends on the quantum mechanics principle known as "Tunneling". In electronics, tunneling means a direct flow of electrons across the small depletion region from n-side conduction band into the p-side valence band.

Germanium material is commonly used to make tunnel diodes. They are also made from other types of materials such as gallium arsenide, gallium antimonide, and silicon.

#### 1.3.2 Width of the Depletion Region in Tunnel Diode:

The depletion region is a region in a p-n junction diode where mobile charge carriers (free electrons and holes) are absent. Depletion region acts like a barrier that opposes the flow of electrons from the n-type semiconductor and holes from the p-type semiconductor.

Figure 1.6 Working of Tunnel Diode

The width of a depletion region depends on the number of impurities added. Impurities are the atoms introduced into the p-type and n-type semiconductor to increase electrical conductivity. If a small number of impurities are added to the p-n junction diode (p-type and n-type semiconductor), a wide depletion region is formed. On the other hand, if large number of impurities are added to the p-n junction diode, a narrow depletion region is formed. In tunnel diode, the p-type and n-type semiconductor is heavily doped which means a large number of impurities are introduced into the p-type and n-type semiconductor. This heavy doping process produces an extremely narrow depletion region. The concentration of impurities in tunnel diode is 1000 times greater than the normal p-n junction diode. In normal p-n junction diode, the depletion width is large as compared to the tunnel diode. This wide depletion layer or depletion region in normal diode opposes the flow of current. Hence, depletion layer acts as a barrier.

To overcome this barrier, need to apply sufficient voltage. When sufficient voltage is applied, electric current starts flowing through the normal p-n junction diode. Unlike the normal p-n junction diode, the width of a depletion layer in tunnel diode is extremely narrow. So applying a small voltage is enough to produce electric current in tunnel diode. Tunnel diodes are capable of remaining stable for a long duration of time than the ordinary p-n junction diodes. They are also capable of high-speed operations.

#### **1.4 PHOTO DIODE:**

A photodiode is a diode working in reverse polarization and having a window where the light can enter and hit directly the p-n junction. As in the case of the LED, the energy level of the impurities has been chosen to allow electrons to jump from valence to conduction band. In the absence of light the leakage current is negligible, but when light is present, the leakage current increases to measurable values.

#### 1.5 TRANSISTORS:

The transistor is the main building block "element" of electronics. It is a semiconductor device and it comes in two general types: the Bipolar Junction Transistor (BJT) and the Field Effect Transistor (FET). Here we will describe the system characteristics of the BJT configuration and explore its use in fundamental signal shaping and amplifier circuits.

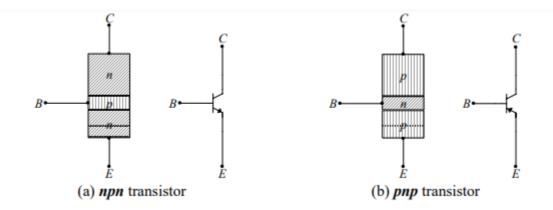

The BJT is a three terminal device and it comes in two different types. The np-n BJT and the p-np BJT. The BJT symbols and their corresponding block diagrams are shown on Figure. The BJT is fabricated with three separately doped regions. The np-n device has one p region between two n regions and the p-np device has one n region between two p regions.

| Analog & Digital Electronics | 1.7 | Advancements in Semiconductor |

|------------------------------|-----|-------------------------------|

|                              |     |                               |

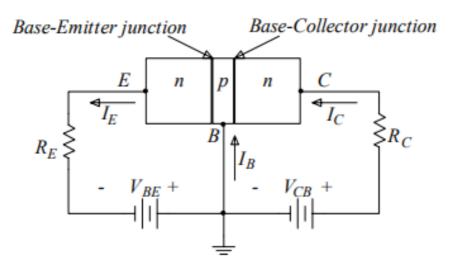

The BJT has two junctions (boundaries between the n and the p regions). These junctions are similar to the junctions we saw in the diodes and thus they may be forward biased or reverse biased. By relating these junctions to a diode model the p-np BJT may be modeled as shown on Figure 1.8.

The three terminals of the BJT are called the Base (B), the Collector (C) and the Emitter (E).

Figure 1.8 BJT schematics and structures. (a) np-n transistor, (b) p-np transistor

Since each junction has two possible states of operation (forward or reverse bias) the BJT with its two junctions has four possible states of operation. For a detailed description of the BJT structure see: Jaeger and Blalock, Microelectronic Circuit Design, McGraw Hill.

Here it is sufficient to say that the structure as shown on Figure .8 is not symmetric. The n and p regions are different both geometrically and in terms of the doping concentration of the regions. For example, doping concentrations in the collector, base and emitter may be, and respectively. Therefore, the behavior of the device is not electrically symmetric and the two ends cannot be interchanged.

Before proceeding let's consider the BJT np-n structure shown on Figure 1.9.

Figure 1.9 Biasing voltages of np-n transistor

Centre for Distance Education 1.8 Acharya Nagarjuna University

#### **1.6 SILICON CONTROLLED RECTIFIER:**

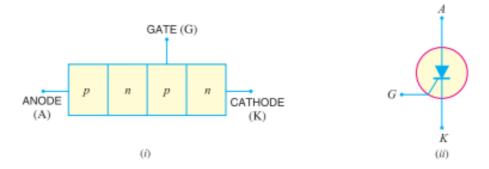

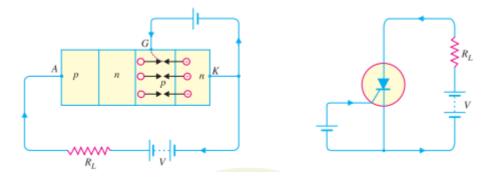

A silicon \*controlled rectifier is a semiconductor \*device that acts as a true electronic switch. It can change alternating current into direct current and at the same time can control the amount of power fed to the load. Thus, SCR combines the features of a rectifier and a transistor.

**Figure 1.10 Silicon Controlled Rectifier**

**Constructional details:** When a p-n junction is added to a junction transistor, the resulting three p-n junction device is called a silicon-controlled rectifier. Figure 1.10 (i) shows its construction. It is clear that it is essentially an ordinary rectifier (p-n) and a junction transistor (np-n) combined in one unit to form p-np-n device. Three terminals are taken; one from the outer p-type material called anode A, second from the outer n-type material called cathode K and the third from the base of transistor section and is called gate G. In the normal operating conditions of SCR, anode is held at high positive potential w.r.t. cathode and gate at small positive potential w.r.t. cathode. Figure 1.10 (ii) shows the symbol of SCR. The silicon-controlled rectifier is a solid state equivalent of thyratron. The gate, anode and cathode of SCR correspond to the grid, plate and cathode of thyratron. For this reason, SCR is sometimes called thyristor.

Figure 1.11 Typical SCR Packages

#### 1.6.1 Working of SCR:

In a silicon-controlled rectifier, load is connected in series with anode. The anode is always kept at positive potential w.r.t. cathode. The working of SCR can be studied under the following two heads:

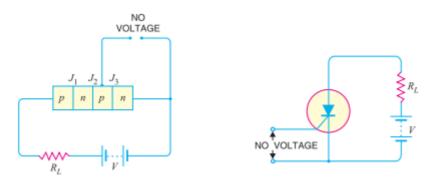

(i) When gate is open the SCR circuit with gate open i.e. no voltage applied to the gate. Under this condition, junction J2 is reverse biased while junctions J1 and J3 are forward biased. Hence, the situation in junctions J1 and J3 is just as in a np-n transistor with base open. Consequently, no current flows through the load RL and the SCR is cut off. However, if the applied voltage is gradually increased, a stage is reached when \* reverse biased junction J2 breaks down. The SCR now conducts \*\* heavily and is said to be in the ON state. The applied voltage at which SCR conducts heavily without gate voltage is called Breakover voltage.

Figure 1.12 SCR Circuit with gate open

(ii) When gate is positive w.r.t. cathode. The SCR can be made to conduct heavily at smaller applied voltage by applying a small positive potential to the gate as shown in Figure 1.13. Now junction J3 is forward biased and junction J2 is reverse biased. The electrons from n-type material start moving across junction J3 towards left whereas holes from p-type towards the right. Consequently, the electrons from junction J3 are attracted across junction J2 and the current gate starts flowing. As soon as the gate current flows, anode current increases. The increased anode current in turn makes more electrons available at junction J2. This process continues and in an extremely small time, junction J2 breaks down and the SCR starts conducting heavily. Once SCR starts conducting, the gate (the reason for this name is obvious) loses all control. Even if gate voltage is removed, the anode current does not decrease at all. The only way to stop conduction (i.e. bring SCR in off condition) is to reduce the applied voltage to zero.

Figure 1.13 Applying small potential to the gate

#### 1.7 SUMMARY:

This study provides an in-depth analysis of semiconductor devices, including diodes, transistors, and silicon-controlled rectifiers (SCRs), focusing on their structure, working principles, and applications. It covers various types of diodes such as p-n junction diodes, tunnel diodes, and photodiodes, explaining their role in rectification, amplification, and switching. The study highlights the impact of doping on the depletion region and how it influences device performance. It also explores the function of transistors, specifically bipolar junction transistors (BJTs), in signal processing and amplification. Additionally, the study examines the operation of SCRs in power control applications, explaining their ability to switch and regulate electrical power efficiently. Special emphasis is given to the tunneling effect in tunnel diodes and the photoelectric effect in photodiodes. Understanding these semiconductor devices is crucial for advancements in modern electronics, as they form the foundation of circuits used in communication, computing, and power management systems.

#### **1.8 TECHNICAL TERMS:**

Diodes, Tunnel diode, Photo diode, Transistor and Silicon controlled rectifier.

#### 1.9 SELF-ASSESSMENT QUESTIONS:

#### **Essay Question:**

- What is the working principle of a p-n junction diode under forward and reverse bias conditions?

- 2) How does a tunnel diode differ from a conventional p-n junction diode, and what is the significance of the tunneling effect?

- 3) What are the main differences between a Bipolar Junction Transistor (BJT) and a Field Effect Transistor (FET)?

#### **Short Notes:**

- 1) How does a photodiode operate, and what role does light play in its functionality?

- 2) What is the structure and working principle of a Silicon Controlled Rectifier (SCR), and how does it control power?

- 3) Why is doping important in semiconductor devices, and how does it affect the depletion region in different diodes?

#### **1.10 SUGGESTED READINGS:**

- "Solid State Electronic Devices" Ben G. Streetman and Sanjay Kumar Banerjee.A fundamental book covering semiconductor physics and various electronic devices like diodes, transistors, and SCRs.

- "Microelectronic Circuits" Adel S. Sedra and Kenneth C. Smith. A comprehensive book explaining the design and analysis of electronic circuits using semiconductor devices.

- "Semiconductor Physics and Devices" Donald A. Neamen. Detailed insights into the physics of semiconductor materials and devices, including p-n junctions, transistors, and tunnel diodes.

- "Electronic Devices and Circuit Theory" Robert L. Boylestad and Louis Nashelsky. A widely used textbook covering the fundamentals of diodes, BJTs, FETs, and other semiconductor devices.

- "Power Electronics: Circuits, Devices, and Applications" Muhammad H. Rashid. A great resource for understanding power semiconductor devices like SCRs, thyristors, and their applications in power control.

**Prof. Sandhya Cole**

#### **LESSON-2**

#### EVOLUTION AND ADVANCEMENTS IN SEMICONDUCTOR DEVICES

#### 2.0 AIM AND OBJECTIVES:

The aim of this document is to provide a comprehensive understanding of semiconductor devices, focusing on Unijunction Transistors (UJT), Field Effect Transistors (FET), Junction Field Effect Transistors (JFET), Metal Oxide Semiconductor Field Effect Transistors (MOSFET), and Complementary Metal Oxide Semiconductor (CMOS) technology. The objective is to explain their construction, working principles, characteristics, and applications in modern electronics. The document explores the fundamental differences between BJTs and FETs, highlighting the advantages of FETs, such as high input impedance and low noise. It also discusses the significance of MOSFETs in integrated circuits and digital logic design, emphasizing the role of CMOS technology in power-efficient semiconductor applications. By detailing these semiconductor components, this document aims to serve as a valuable resource for students, researchers, and professionals seeking a deeper understanding of transistor technology and its impact on electronic circuit design.

#### **STRUCTURE:**

- 2.1 Uni junction transistor

- 2.2 Field effect transistor

- **2.3 JFET**

- 2.4 MOSFET

- 2.5 CMOS

- 2.6 Summary

- 2.7 Technical Terms

- 2.8 Self-Assessment Questions

- 2.9 Suggested Readings

#### 2.1 UNI JUNCTION TRANSISTOR:

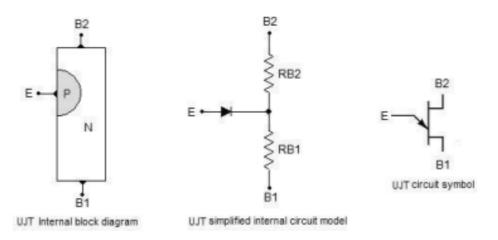

Unijunction transistor (abbreviated as UJT), also called the double-base diode is a 2- layer, 3-terminal solid-state (silicon) switching device. The device has a unique characteristic that when it is triggered, its emitter current increases re generatively (due to negative resistance

characteristic) until it is restricted by emitter power supply. Since the device has one p n junction and three leads p n junction and three leads

Figure 2.1 UJT Structure, Equivalent Circuit and Symbol

### 2.1.1 Construction of a UJT:

The basic structure of a unijunction transistor is shown in figure. It essentially consists of a lightly-doped N-type silicon bar with a small piece of heavily doped P-type material alloyed to its one side to produce single P-N junction. The single P-N junction accounts for the terminology unijunction. The silicon bar, at its ends, has two ohmic contacts designated as base-1 (B1) and base-2 (B2), as shown and the P-type region is termed the emitter (E). The emitter junction is usually located closer to base-2 (B2) than base-1 (B1) so that the device is not symmetrical, because symmetrical unit does not provide optimum electrical characteristics for most of the applications.

The symbol for unijunction transistor is shown in figure 2.1. The emitter leg is drawn at an angle to the vertical line representing the N-type material slab and the arrowhead points in the direction of conventional current when the device is forward-biased, active or in the conducting state. The basic arrangement for the UJT is shown in figure. A complementary UJT is formed by diffusing an N-type emitter terminal on a P-type base. Except for the polarities of voltage and current, the characteristics of a complementary UJT are exactly the same as those of a conventional UJT.

- The device has only one junction, so it is called the unijunction device.

- The device, because of one P-N junction, is quite similar to a diode but it differs from an ordinary diode as it has three terminals.

- The structure of a UJT is quite similar to that of an N-channel JFET. The main difference is that P-type (gate) material surrounds the N-type (channel) material in case of JFET and the gate surface of the JFET is much larger than emitter junction of UJT.

2.2

- In a unijunction transistor the emitter is heavily doped while the N-region is lightly doped, so the resistance between the base terminals is relatively high, typically 4 to 10 kilo Ohm when the emitter is open.

- The N-type silicon bar has a high resistance and the resistance between emitter and base-1 is larger than that between emitter and base-2. It is because emitter is closer to base-2 than base-1.

- UJT operates with emitter junction forward- biased while the JFET is normally operated with the gate junction reverse-biased.

- UJT does not have ability to amplify but it has the ability to control a large ac power with a small signal. It exhibits a negative resistance characteristic and so it can be employed as an oscillator.

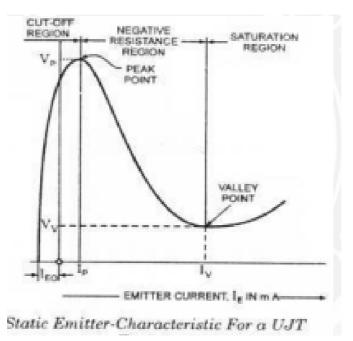

#### 2.1.2 UJT Characteristics:

Figure 2.2 Static Emitter Characteristic for a UJT

The static emitter characteristic (a curve showing the relation between emitter voltage VE and emitter current IE) of a UJT at a given inter base voltage VBB is shown in figure. From figure it is noted that for emitter potentials to the left of peak point, emitter current IE never exceedsIEo. The current IEo corresponds very closely to the reverse leakage current ICo of the conventional BJT. This region, as shown in the figure, is called the cut-off region. Once conduction is established at VE = VP the emitter potential VE starts decreasing with the increase in emitter current IE. This Corresponds exactly with the decrease in resistance RB for increasing current IE. This device, therefore, has a negative resistance region which is stable enough to be used with a great

deal of reliability in the areas of applications listed earlier. Eventually, the valley point reaches, and any further increase in emitter current IE places the device in the saturation region, as shown in the figure 2.2. Three other important parameters for the UJT are IP, VV and IV and are defined below:

2.4

- a) **Peak-Point Emitter Current Ip**: It is the emitter current at the peak point. It represents the minimum current that is required to trigger the device (UJT). It is inversely proportional to the inter base voltage VBB.

- **b) Valley Point Voltage V:** The valley point voltage is the emitter voltage at the valley point. The valley voltage increases with the increase in inter base voltage VBB.

- c) Valley Point Current IV: The valley point current is the emitter current at the valley point. It increases with the increase in inter-base voltage VBB.

## 2.1.3 Applications of UJT:

- Relaxation oscillators.

- Switching Thyristors like SCR, TRIAC etc.

- Magnetic flux sensors.

- Voltage or current limiting circuit.

- Bistable oscillators.

- Voltage or current regulators.

- Phase control circuits.

## 2.2 FIELD EFFECT TRANSISTOR:

The field effect transistor (FET) has, by virtue of its construction and biasing, large input impedance which may be more than 100 megaohms. The FET is generally much less noisy than the ordinary or bipolar transistor. The rapidly expanding FET market has led many semiconductor marketing managers to believe that this device will soon become the most important electronic device, primarily because of its integrated-circuit applications. In this chapter, we shall focus our attention on the construction, working and circuit applications of field effect transistors.

## 2.2.1 Types of Field Effect Transistors:

A bipolar junction transistor (BJT) is a current controlled device i.e., output characteristics of the device are controlled by base current and not by base voltage. However, in a field effect transistor (FET), the output characteristics are controlled by

input voltage (i.e., electric field) and not by input current. This is probably the biggest difference between BJT and FET. There are two basic types of field effect transistors:

(i) Junction field effect transistor (JFET) (ii) Metal oxide semiconductor field effect transistor (MOSFET) To begin with, we shall study about JFET and then improve form of JFET, namely; MOSFET.

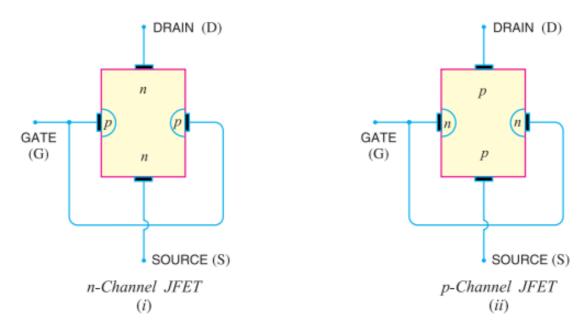

#### **2.3 JFET:**

A junction-field effect transistor is a three-termsemi-conductor device in which current conduction is by one type of carrier i.e., electrons or holes.

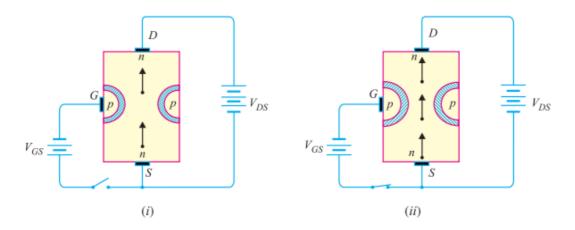

The JFET was developed at about the same time as the transistor, but it came into general use only in the late 1960s. In a JFET, the current conduction is either by electrons or holes and is controlled by means of an electric field between the gate electrode and the conducting channel of the device. The JFET has high input impedance and low noise level. Constructional details. A JFET consists of a p-type or n-type silicon bar containing two pn junctions at the sides as shown in Figure 2.3. The bar forms the conducting channel for the charge carriers. If the bar is of n-type, it is called n-channel JFET as shown in Figure2.3 (i) and if the bar is of p-type, it is called a p-channel JFET as shown in Figure2.3 (ii). The two pn junctions forming diodes are connected \*internally and a common terminal called gate is taken out. Other terminals are source and drain taken out from the bar as shown. Thus, a JFET has essentially three terminals viz., gate (G), source (S) and drain (D).

**Figure 2.3: JFET Channels**

## 2.3.1 Principle and Working of JFET:

Figure 2.4 shows the circuit of n-channel JFET with normal polarities. Note that the gate is reverse biased.

**a. Principle.** The two pn junctions at the sides form two depletion layers. The current conduction by charge carriers (i.e. free electrons in this case) is through the channel between the two depletion layers and out of the drain. The width and hence \*resistance of this channel can be controlled by changing the input voltage VGS. The greater the reverse voltage of VGS, the wider the depletion layers will be and the narrowerthe conducting channel will be. The narrower channel means greater resistance and hence sources to drain current decreases. The reverse will happen should VGS decrease. Thus, JFET operates on the principle that width and hence resistance of the conducting channel can be varied by changing the reverse VGS. In other words, the magnitude of drain current (ID) can be changed by altering VGS.

**Working:** The working of JFET is as under:

- (i) When a voltage VDS is applied between drain and source terminals and voltage on the gate is zero [See Figure 2.4 (i) ], the two pn junctions at the sides of the bar establish depletion layers. The electrons will flow from source to drain through a channel between the depletion layers. The size of these layers determines the width of the channel and hence the current conduction through the bar.

- (ii) When a reverse voltage VGS is applied between the gate and source [See Figure 2.4 (ii)], the width of the depletion layers is increased. This reduces the width of conducting channels, thereby increasing the resistance of n-type bar. Consequently, the current from source to drain is decreased. On the other hand, if the reverse voltage on the gate is decreased, the width of the depletion layers also decreases. This increases the width of the conducting channel and hence sources drain current.

Figure 2.4: Principle and Working of JFET

It is clear from the above discussion that current from source to drain can be controlled by the application of potential (i.e. electric field) on the gate. For this reason, the device is called a field effect transistor. It may be noted that a p-channel JFET operates in the same manner as an n -channel JFET except that channel current carriers will be the holes instead of electrons and the polarities of VGS and VDS are reversed.

2.7

JFET biased for Conduction

#### Figure 2.5 JFET biased for Conduction

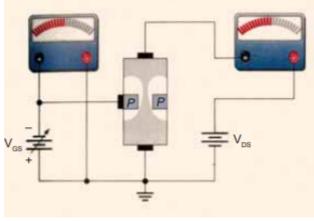

#### 2.3.2 Schematic Symbol of JFET:

Figure 1.5 shows the schematic symbol of JFET. The vertical line in the symbol may be thought of as channel and source (S) and drain (D) connected to this line. If the channel is n-type, the arrow on the gate points towards the channel as shown in Figure 2.6 (i). However, for p-type channel, the arrow on the gate points from channel to gate [See Figure 2.6 (ii)].

#### **Figure 2.6 Schematic Symbol of JFET**

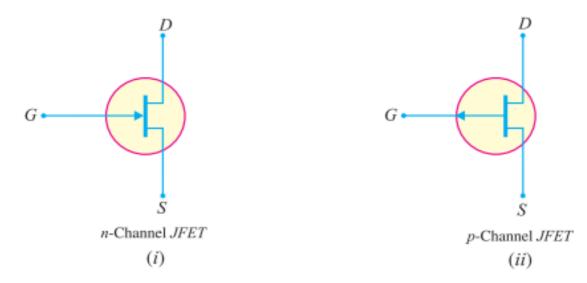

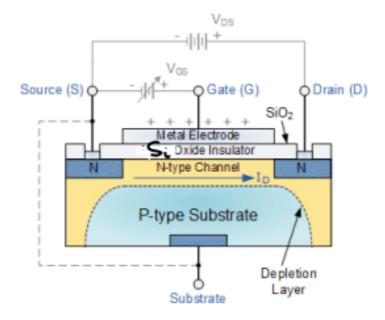

#### 2.4 MOSFET:

MOSFET's operate the same as JFET's but have a gate terminal that is electrically isolated from the conductive channel.

Figure 2.7: JFET Gate Terminal

As well as the Junction Field Effect Transistor (JFET), there is another type of Field Effect Transistor available whose Gate input is electrically insulated from the main current carrying channel and is therefore called an Insulated Gate Field Effect Transistor. The most common type of insulated gate FET which is used in many different types of electronic circuits is called the Metal Oxide Semiconductor Field Effect Transistor or MOSFET for short.

The IGFET or MOSFET is a voltage-controlled field effect transistor that differs from a JFET in that it has a "Metal Oxide" Gate electrode which is electrically insulated from the main semiconductor n-channel or p-channel by a very thin layer of insulating material usually silicon dioxide, commonly known as glass. This ultra-thin insulated metal gate electrode can be thought of as one plate of a capacitor. The isolation of the controlling Gate makes the input resistance of the MOSFET extremely high way up in the Mega-ohms (M $\Omega$ ) region thereby making it almost infinite.

As the Gate terminal is electrically isolated from the main current carrying channel between the drain and source, "NO current flows into the gate" and just like the JFET, the MOSFET also acts like a voltage-controlled resistor where the current flowing through the main channel between the Drain and Source is proportional to the input voltage. Also like the JFET, the MOSFETs' very high input resistance can easily accumulate large amounts of static charge resulting in the MOSFET becoming easily damaged unless carefully handled or protected. Like the previous JFET tutorial, MOSFETs are three terminal devices with a Gate, Drain and Source and both P-channel (PMOS) and N-channel (NMOS) MOSFETs are available. The main difference this time is that MOSFETs are available in two basic forms:

Depletion Type – the transistor requires the Gate-Source voltage, (V) to switch the device "OFF". The depletion mode MOSFET is equivalent to a "Normally Closed" switch.

Enhancement Type – the transistor requires a Gate-Source voltage, (V) to switch the device "ON". The enhancement mode MOSFET is equivalent to a "Normally Open" switch.

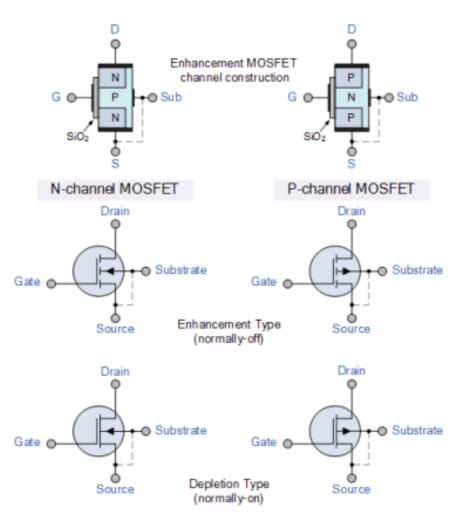

The symbols and basic construction for both configurations of MOSFETs are shown below.

Figure 2.8: The Symbols and Basic Construction for Both Configurations of MOSFETs

The four MOSFET symbols above show an additional terminal called the Substrate and is not normally used as either an input or an output connection but instead it is used for grounding the substrate. It connects to the main semiconductive channel through a diode junction to the body or metal tab of the MOSFET.

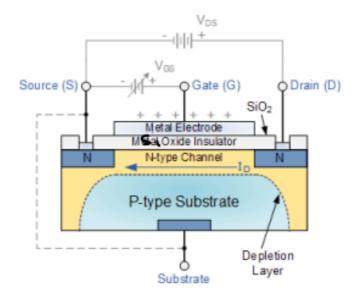

#### 2.4.1 Basic MOSFET Structure and Symbol:

Figure 2.9 Basic MOSFET structure and Symbol

The construction of the Metal Oxide Semiconductor FET is very different to that of the Junction FET. Both the Depletion and Enhancement type MOSFETs use an electrical field produced by a gate voltage to alter the flow of charge carriers, electrons for n-channel or holes for P-channel, through the semiconductive drain-source channel. The electrode gate is placed on top of a very thin insulating layer and there are a pair of small n-type regions just under the drain and source electrodes. We saw in the previous tutorial that the gate of a junction field effect transistor, JFET must be biased in such a way as to reverse-bias the pn-junction.

With a insulated gate MOSFET device no such limitations apply so it is possible to bias the gate of a MOSFET in either polarity, positive (+ve) or negative (-ve). This makes the MOSFET device especially valuable as electronic switches or to make logic gates because with no bias they are normally non-conducting, and this high gate input resistance means that very little or no control current is needed as MOSFETs are voltage-controlled devices. Both the p-channel and the n-channel MOSFETs are available in two basic forms, the Enhancement type and the Depletion type.

## 2.5 CMOS:

#### 2.5.1 CMOS Working Principle and Applications:

The term CMOS stands for "Complementary Metal Oxide Semiconductor". CMOS technology is one of the most popular technologies in the computer chip design industry and broadly used today to form integrated circuits in numerous and varied applications. Today's

computer memory, CPUs and cell phones make use of this technology due to several key advantages. This technology makes use of both P channel and N channel semiconductor devices.

One of the most popular MOSFET technologies available today is the Complementary MOS or CMOS technology. This is the dominant semiconductor technology for microprocessors, microcontroller chips, memory like RAM, ROM, EEPROM and application specific integrated circuits (ASICs).

## 2.5.2 CMOS (Complementary Metal Oxide Semiconductor):

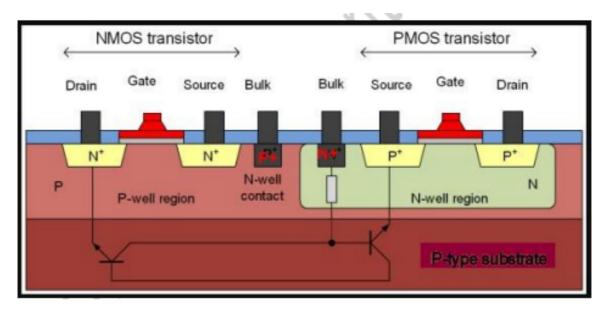

The main advantage of CMOS over NMOS and BIPOLAR technology is the much smaller power dissipation. Unlike NMOS or BIPOLAR circuits, a Complementary MOS circuit has almost no static power dissipation. Power is only dissipated in case the circuit actually switches. This allows integrating more CMOS gates on an IC than in NMOS or bipolar technology, resulting in much better performance. Complementary Metal Oxide Semiconductor transistor consists of P-channel MOS (PMOS) and Nchannel MOS (NMOS). Please refer the link to know more about the fabrication process of CMOS transistor.

Figure 2.10: NMOS Transistor and PMOS Transistor

## 2.5.2.1 NMOS:

NMOS is built on a p-type substrate with n-type source and drain diffused on it. In NMOS, the majority carriers are electrons. When a high voltage is applied to the gate, the NMOS will conduct. Similarly, when a low voltage is applied to the gate, NMOS will not conduct. NMOS are faster than PMOS, since the carriers in NMOS, which are electrons, travel twice as fast as the holes.

NMOS Transistor

#### Figure 2.11 NMOS Transistor

#### 2.5.2.2 PMOS:

P-channel MOSFET consists of P-type Source and Drain diffused on an N-type substrate. Majority carriers are holes. When a high voltage is applied to the gate, the PMOS will not conduct. When a low voltage is applied to the gate, the PMOS will conduct. The PMOS devices are more immune to noise than NMOS devices.

**PMOS Transistor**

Figure 2.12 PMOS Transistor

#### 2.5.3 CMOS Working Principle:

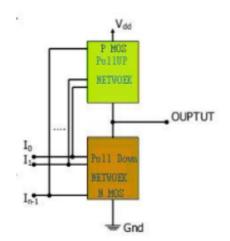

In CMOS technology, both N-type and P-type transistors are used to design logic functions. The same signal which turns ON a transistor of one type is used to turn OFF a transistor of the other type. This characteristic allows the design of logic devices using only simple switches, without the need for a pullup resistor. In CMOS logic gates a collection of n-type MOSFETs is arranged in a pull-down network between the output and the low voltage power supply rail (Vss or quite often ground).

Instead of the load resistor of NMOS logic gates, CMOS logic gates have a collection of ptype MOSFETs in a pull-up network between the output and the higher-voltage rail (often named Vdd). Thus, if both a p-type and n-type transistor have their gates connected to the same input, the p-type MOSFET will be ON when the n-type MOSFET is OFF, and viceversa. The networks are arranged such that one is ON and the other OFF for any input pattern as shown in the figure below.

### Figure 2.13: MOSFET Arranged Networks

#### 2.5.4 CMOS Logic Gate using Pull-Up and Pull-Down Networks:

CMOS offers relatively high speed, low power dissipation, high noise margins in both states, and will operate over a wide range of source and input voltages (provided the source voltage is fixed). Furthermore, for the better understanding of the Complementary Metal Oxide Semiconductor working principle, we need to discuss in brief about CMOS logic gates as explained below.

#### 2.6 SUMMARY:

This document provides a detailed overview of semiconductor devices, focusing on Unijunction Transistors (UJT), Field Effect Transistors (FET), Junction Field Effect Transistors (JFET), Metal Oxide Semiconductor Field Effect Transistors (MOSFET), and Complementary Metal Oxide Semiconductor (CMOS) technology. It explains their construction, working principles, characteristics, and applications in modern electronics. The document highlights the differences between Bipolar Junction Transistors (BJT) and FETs, emphasizing FETs' advantages such as high input impedance and low noise. It also explores the critical role of MOSFETs in integrated circuits and digital logic, particularly in CMOS technology, which enables power-efficient semiconductor applications. By covering these essential semiconductor components, this document serves as a valuable resource for students, researchers, and professionals interested in electronic circuit design. Understanding these devices is crucial for advancements in microelectronics, computing, and communication technologies, making this study an essential foundation for future innovations in the semiconductor industry.

## 2.7 TECHNICAL TERMS:

JFET, UJT, FET, CMOS, MOSFET

#### 2.8 SELF-ASSESSMENT QUESTIONS:

#### **Essay Questions:**

- 1) What are the key differences between Bipolar Junction Transistors (BJT) and Field Effect Transistors (FET)?

- 2) How does Unijunction Transistor (UJT) function, and what are its primary applications?

- 3) What are the advantages of using a Junction Field Effect Transistor (JFET) over a BJT?

#### **Short Answer Questions:**

- 1) How does a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) operate, and why is it widely used in modern electronics?

- 2) What is Complementary Metal Oxide Semiconductor (CMOS) technology, and how does it contribute to power efficiency in digital circuits?

- 3) Why is understanding semiconductor devices essential for advancements in microelectronics and communication technologies?

#### 2.9 SUGGESTED READINGS:

- 1) "Semiconductor Physics and Devices" Donald A. Neamen.

- 2) "Solid State Electronic Devices" Ben G. Streetman & Sanjay Kumar Banerjee.

- 3) "Microelectronic Circuits" Adel S. Sedra & Kenneth C. Smith.

- 4) "Fundamentals of Microelectronics" Behzad Razavi.

- 5) "Physics of Semiconductor Devices" Simon M. Sze & Kwok K. Ng.

- 6) "Electronic Devices and Circuit Theory" Robert L. Boylestad & Louis Nashelsky.

- 7) "Introduction to Semiconductor Devices" Kevin F. Brennan.

#### **Prof. Sandhya Cole**

### **LESSON-3**

#### **OPTO ELECTRONIC DEVICES**

#### **3.0 AIM AND OBJECTIVES:**

The aim of this study is to explore the working principles, construction, and materials used in solar cells, photo detectors, and LEDs, focusing on their significance in energy conversion and optical communication. Solar cells, which convert light energy into electrical energy through the photovoltaic effect, are primarily made using semiconductor materials like silicon, GaAs, CdTe, and CuInSe<sub>2</sub>, chosen for their suitable band gaps. Photodetectors, particularly PIN and avalanche photodiodes (APD), play a crucial role in fiber-optic communication by converting light signals into electrical signals with high sensitivity. LEDs, operating on the principle of electroluminescence, emit visible or infrared light based on the material used, with applications ranging from display systems to optical sensors. Understanding the relationship between material properties and device performance is essential for optimizing efficiency in renewable energy generation, optical data transmission, and solid-state lighting. This study aims to provide a comprehensive understanding of these semiconductor devices, highlighting their construction, functionality, and advancements that contribute to energy-efficient technologies and high-speed communication systems.

#### **STRUCTURE:**

- **3.2** Photo detectors

- 3.3 LEDs

- 3.4 Visible LEDs and invisible LEDs

- 3.5 Summary

- 3.6 Technical Terms

- 3.7 Self-Assessment Questions

- 3.8 Suggested Readings

#### **3.1 SOLAR CELLS:**

A solar cell (also known as a photovoltaic cell or PV cell) is defined as an electrical device that converts light energy into electrical energy through the photovoltaic effect. A solar cell is basically a p-n junction diode. Solar cells are a form of photoelectric cell, defined as a device whose electrical characteristics – such as current, voltage, or resistance – vary when exposed to light.

Individual solar cells can be combined to form modules commonly known as solar panels. The common single junction silicon solar cell can produce a maximum opencircuit voltage of approximately 0.5 to 0.6 volts. By itself this isn't much – but remember these solar cells are tiny. When combined into a large solar panel, considerable amounts of renewable energy can be generated.

#### **3.1.1 Construction of Solar Cell:**

A solar cell is basically a junction diode, although its construction is little bit different from conventional p-n junction diodes. A very thin layer of p-type semiconductor is grown on a relatively thicker n-type semiconductor. We then apply a few finer electrodes on the top of the p-type semiconductor layer.

These electrodes do not obstruct light to reach the thin p-type layer. Just below the ptype layer there is a p-n junction. We also provide a current collecting electrode at the bottom of the n-type layer. We encapsulate the entire assembly by thin glass to protect the solar cell from any mechanical shock.

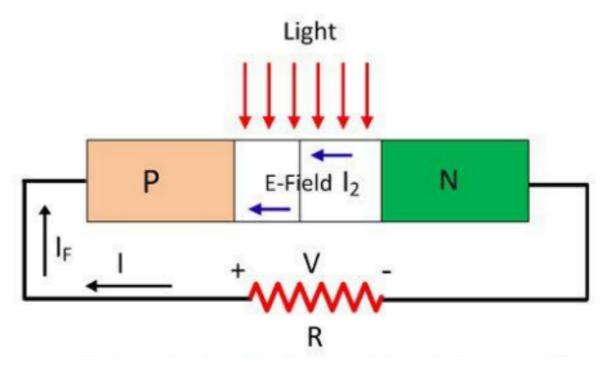

Figure 3.1 P-N Junction Solar Cell with Resistive Load

## 3.1.2 Working Principle of Solar Cell:

When light reaches the p-n junction, the light photons can easily enter in the junction, through a very thin p-type layer. The light energy, in the form of photons, supplies sufficient energy to the junction to create several electron-hole pairs. The incident light breaks the thermal equilibrium condition of the junction. The free electrons in the depletion region can quickly come to the n-type side of the junction.

Similarly, the holes in the depletion can quickly come to the p-type side of the junction. Once, the newly created free electrons come to the n-type side, cannot further cross the junction because of barrier potential of the junction.

Similarly, the newly created holes once come to the p-type side cannot further cross the junction became of same barrier potential of the junction. As the concentration of electrons become higher in one side, i.e. n-type side of the junction and concentration of holes becomes more in another side, i.e. the p-type side of the junction, the p-n junction will behave like a small battery cell. A voltage is set up which is known as photo voltage. If we connect a small load across the junction, there will be a tiny current flowing through it.

## 3.1.3 Materials Used in Solar Cell:

The materials which are used for this purpose must have a band gap close to 1.5ev. The commonly used materials are

- 1) Silicon

- 2) GaAs

- 3) CdTe

- 4) CuInSe2

## **3.2 PHOTO DETECTORS:**

- A photo detector is a device which converts the light signals to electrical signals.

- The two main photo detectors used for fiber communication system are,

- 1) PIN photo diode

- 2) Avalanche photo diode (APD)

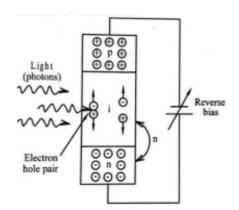

#### 3.2.1 Pin Photo Diode:

#### 3.2.1.1 Principle:

- Reverse bias is applied to a diode.

- Light is allowed to fall on the neutral (or) intrinsic'i' region, electron hole pairs are generated.

- These electrons and holes are accelerated by the external electric field, which results in photo current.

- Thus, light is converted into electrical signals.

3.3

Figure 3.2: PIN Photo Diode

#### **3.2.1.2 Construction:**

- 1) It consists of 'p' and 'n' regions separated by an intrinsic region 'i'.

- 'p' and 'n' regions are made by silicon, germanium and their alloys and they are heavily doped.

- 3) i' region is lightly doped by 'n' material and made as large as possible to absorb more photons.

- 4) So, it is called as positive-intrinsic-negative (PIN) photo diode.

#### 3.2.1.3 Working:

- 1) When a high reverse bias voltage is applied, the width of the depletion (neutral) region gets increased.

- 2) When a photon of energy is greater than or equal to the band gap energy of the photo diode incidents on the depletion region, the electron hole pairscreated due to the absorption of photon.

- 3) The mobile charges are accelerated by the applied voltage which gives photo current in external circuit.

- 4) It acts as a linear device because the photo current is directly proportional to the optical power incident.

#### 3.3 LEDs:

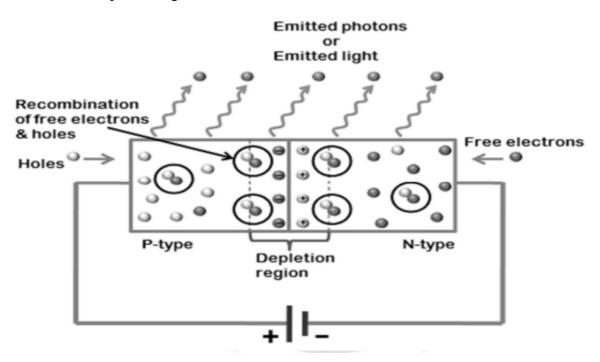

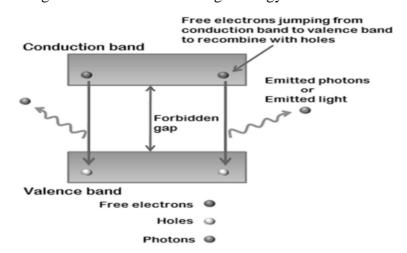

Light Emitting Diode (LED) works only in forward bias condition. When Light Emitting Diode (LED) is forward biased, the free electrons from n-side and the holes from p-side are pushed towards the junction.

When free electrons reach the junction or depletion region, some of the free electrons recombine with the holes in the positive ions. We know that positive ions have less electrons than protons. Therefore, they are ready to accept electrons. Thus, free electrons recombine with holes in the depletion region. In a similar way, holes from the p-side recombine with electrons in the depletion region.

Figure 3.3: Working of Light Emitting Diode

Because of the recombination of free electrons and holes in the depletion region, the width of depletion region decreases. As a result, more charge carriers will cross the p-n junction.

Some of the charge carriers from p-side and n-side will cross the p-n junction before they recombine in the depletion region. For example, some free electrons from n-type semiconductors cross the p-n junction and recombine with holes in p-type semiconductor. In a similar way, holes from p-type semiconductors cross the p-n junction and combine with free electrons in the n-type semiconductor.

Thus, recombination takes place in depletion region as well as in p-type and n-type semiconductor. The free electrons in the conduction band releases energy in the form of light before they recombine with holes in the valence band.

In silicon and germanium diodes, most of the energy is released in the form of heat and emitted light is too small. However, in materials like gallium arsenide and gallium phosphide the emitted photons have sufficient energy to produce intense visible light. When external voltage is applied to the valence electrons, they gain sufficient energy and break the bonding with the parent atom. The valence electrons which break bonding with the parent atom are called free electrons. When the valence electron left the parent atom, they leave an

| Centre for Distance Education 3.6 A | Acharya Nagarjuna University |

|-------------------------------------|------------------------------|

|-------------------------------------|------------------------------|

empty space in the valence shell at which valence electron left. This empty space in the valence shell is called a hole. The energy level of all the valence electrons is almost the same.

Grouping the range of energy levels of all the valence electrons is called valence band. In a similar way, energy level of all the free electrons is almost same. Grouping the range of energy levels of all the free electrons is called conduction band. The energy level of free electrons in the conduction band is high compared to the energy level of valence electrons or holes in the valence band. Therefore, free electrons in the conduction band need to lose energy to recombine with the holes in the valence band. The free electrons in the conduction band do not stay for long periods. After a short period, the free electrons lose energy in the form of light and recombine with the holes in the valence band. Each recombination of charge carrier will emit some light energy.

Figure 3.4 Process of Light Emission in LED

The energy loss of free electrons or the intensity of emitted light depends on the forbidden gap or energy gap between conduction band and valence band. The semiconductor device with large forbidden gap emits high intensity light whereas the semiconductor device with small forbidden gap emits low intensity light. In other words, the brightness of the emitted light depends on the material used for constructing LED and forward current flow through the LED. In normal silicon diodes, the energy gap between conduction band and valence band is less.

Hence, the electrons fall only a short distance. As a result, low energy photons are released. These low energy photons have low frequency which is invisible to the human eye. In LEDs, the energy gap between conduction band and valence band is very large so the free electrons in LEDs have greater energy than the free electrons in silicon diodes. Hence, the free electrons fall to a large distance. As a result, high energy photons are released. These high energy photons have high frequency which is visible to the human eye. The efficiency of the generation of light in LED increases with increase in injected current and with a decrease in temperature. In light emitting diodes, light is produced due to the recombination process.

| Analog | & | Digital | l Electroni | cs |

|--------|---|---------|-------------|----|

|--------|---|---------|-------------|----|

Recombination of charge carriers takes place only under forward bias conditions. Hence, LEDs operate only in forward bias condition.

When light emitting diode is reverse biased, the free electrons (majority carriers) from nside and holes (majority carriers) from p-side moves away from the junction. As a result, the width of depletion region increases, and no recombination of charge carriers occurs. Thus, no light is produced. If the reverse bias voltage applied to the LED is highly increased, the device may also be damaged. All diodes emit photons or light, but not all diodes emit visible light. The material in an LED is selected in such a way that the wavelength of the released photons falls within the visible portion of the light spectrum. Light emitting diodes can be switched ON and OFF at a very fast speed of 1 ns.

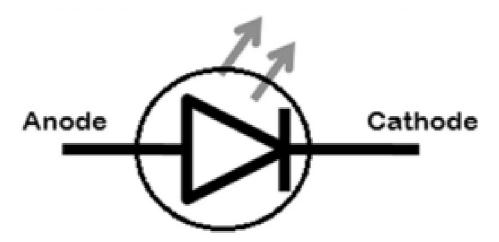

## 3.3.1 Light Emitting Diode (LED) Symbol:

The symbol of LED is like the normal p-n junction diode except that it contains arrows pointing away from the diode indicating that light is being emitted by the diode.

Figure 3.5 Symbol of Light Emitting Diode

LEDs are available in different colors. The most common colors of LEDs are orange, yellow, green and red. The schematic symbol of LED does not represent the color of light. The schematic symbol is the same for all colors of LEDs. Hence, it is not possible to identify the color of LED by seeing its symbol.

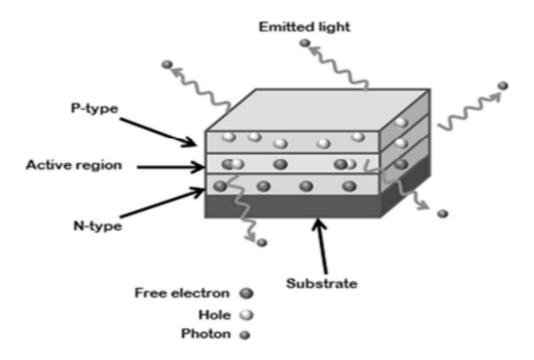

## 3.3.2 LED Construction:

One of the methods used to construct LED is to deposit three semiconductor layers on the substrate. The three semiconductor layers deposited on the substrate are n-type semiconductor, p-type semiconductor and active region. Active region is present in between the n-type and p-type semiconductor layers.

Figure 3.6 Construction of Light Emitting Diode

When LED is forward biased, free electrons from n-type semiconductor and holes from p-type semiconductor are pushed towards the active region. When free electrons from n-side and holes from p-side recombine with the opposite charge carriers (free electrons with holes or holes with free electrons) in active region, an invisible or visible light is emitted. In LED, most of the charge carriers recombine at active region. Therefore, most of the light is emitted by the active region. The active region is also called depletion region.

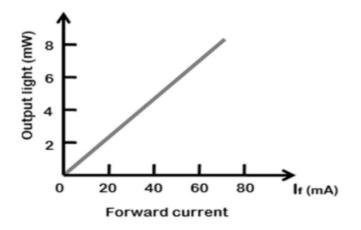

#### 3.3.3 Output Characteristics of LED:

The amount of output light emitted by the LED is directly proportional to the amount of forward current flowing through the LED. The more forward the current, the greater the output light is emitted. The graph of forward current vs output light is shown in figure 3.7.

Figure 3.7 Characteristics of Light Emitting Diode

## 3.4 VISIBLE LED'S AND INVISIBLE LED'S:

LEDs are mainly classified into two types: visible LEDs and invisible LEDs. Visible LED is a type of LED that emits visible light. These LEDs are mainly used for display or illumination where LEDs are used individually without photosensors. Invisible LED is a type of LED that emits invisible light (infrared light). These LEDs are mainly used with photosensors such as photodiodes.

## **3.4.1 Determines the Color of an LED:**

The material used for constructing LED determines its color. In other words, the wavelength or color of the emitted light depends on the forbidden gap or energy gap of the material. Different materials emit different colors of light. Gallium arsenide LEDs emit red and infrared light. Gallium nitride LEDs emit bright blue light. Yttrium aluminium garnet LEDs emit white light. Gallium phosphide LEDs emit red, yellow and green light. Aluminium gallium nitride LEDs emit ultraviolet light. Aluminum gallium phosphide LEDs emit green light.

## 3.5 SUMMARY:

This study explores the principles, construction, and materials used in solar cells, photo detectors, and LEDs, highlighting their importance in energy conversion and optical communication. Solar cells, based on the photovoltaic effect, generate electricity from light using materials like silicon, GaAs, CdTe, and CuInSe<sub>2</sub>. Photodetectors, including PIN and avalanche photodiodes, convert light signals into electrical signals, playing a vital role in fiber-optic communication. LEDs function through electroluminescence, emitting visible or infrared light depending on the semiconductor material used, with applications in displays, lighting, and sensors. The efficiency of these devices is influenced by material properties such as band gaps and doping. Understanding their working mechanisms and material selection helps enhance performance in renewable energy, high-speed communication, and solid-state lighting. This study provides a detailed insight into these semiconductor devices, emphasizing their role in advancing modern technology and promoting energy-efficient solutions.

#### **3.6 TECHNICAL TERMS:**

Photovoltaic Effect, Band Gap, Electroluminescence, Depletion Region, Quantum Efficiency

## 3.7 SELF-ASSESSMENT QUESTIONS:

#### **Essay Questions:**

1) What is the photovoltaic effect, and how does it enable solar cells to generate electricity?

- 2) How does the band gap of a semiconductor material influence the efficiency of solar cells, photodetectors, and LEDs?

- 3) What is electroluminescence, and why is it essential for the functioning of LEDs?

#### **Short Answer Questions:**

- 1) How does the depletion region in a p-n junction semiconductor affect the performance of solar cells and photodetectors?

- 2) What are the key differences between PIN photodiodes and avalanche photodiodes in optical communication systems?

- 3) How does quantum efficiency impact the performance of solar cells and photodetectors?

#### **3.8 SUGGESTED READINGS:**

- 1) S.M. Sze and K.K. Ng, Physics of Semiconductor Devices, 3rd Ed. Hoboken, NJ, USA: Wiley, 2007.

- 2) J. Nelson, The Physics of Solar Cells. London, UK: Imperial College Press, 2003.

- 3) Rogalski, Semiconductor Optoelectronic Devices: Introduction to Physics and Applications, 2nd ed. Boca Raton, FL, USA: CRC Press, 2020.

- 4) M.A. Green, Solar Cells: Operating Principles, Technology and System Applications. Englewood Cliffs, NJ, USA: Prentice Hall, 1982.

- 5) G. Streetman and S. Banerjee, Solid State Electronic Devices, 7<sup>th</sup> Ed. Upper Saddle River, NJ, USA: Pearson, 2014.

**Prof. Sandhya Cole**

## **LESSON-4**

## **OPERATIONAL AMPLIFIERS**

#### 4.0 AIM AND OBJECTIVES:

The aim of this lesson is to understand the fundamental concepts, configurations, and applications of operational amplifiers (Op-Amps), focusing on differential amplifiers as their core building blocks. The lesson explores various circuit configurations, including dual-input balanced output differential amplifiers, and provides both DC and AC analysis to understand their operational behavior. It also covers critical parameters such as common-mode rejection ratio (CMRR), inverting and non-inverting inputs, and voltage gain calculations. By the end of this lesson, learners will be able to analyze and design differential amplifier circuits, comprehend the working principles of Op-Amps, and apply this knowledge to real-world applications. Additionally, students will gain insights into the block diagram representation of a typical Op-Amp and its practical significance in analog electronics, including amplification, filtering, and signal processing.

#### **STRUCTURE:**

- 4.1 Differential Amplifiers

- 4.2 Circuit configurations

- 4.3 Dual input- Balanced output differential amplifier

- 4.4 DC analysis

- 4.5 AC analysis

- 4.6 Inverting and non-inverting inputs CMRR

- 4.7 Block diagram of a typical Op-Amp-analysis

- 4.8 Summary

- 4.9 Technical Terms

- 4.10 Self-Assessment Questions

- 4.11 Suggested Readings

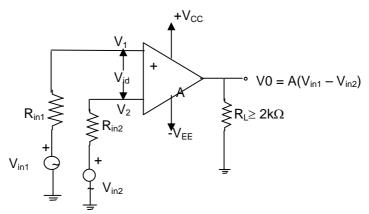

#### 4.1 **DIFFERENTIAL AMPLIFIERS:**

The differential amplifier, also called a difference amplifier, as the name implies, amplifies the difference between two signals. Because of its balanced nature and symmetry, it can amplify very small signals. It usually requires a minimum number of capacitors and can operate without bypassing and coupling capacitors. It is the basic building block of operational amplifiers, which are most widely used in integrated circuits.

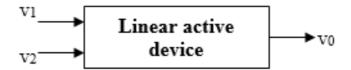

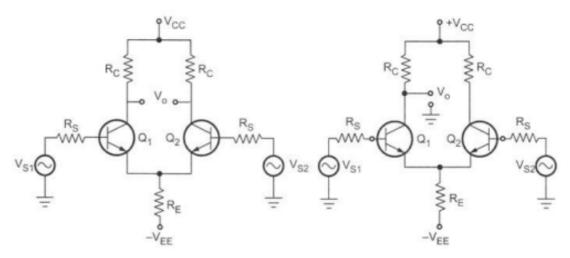

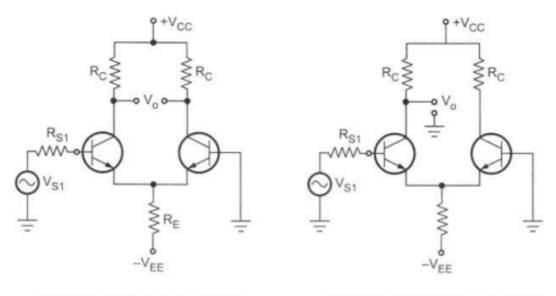

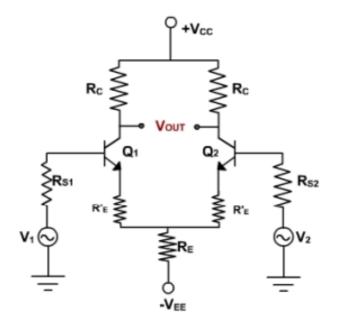

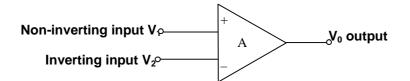

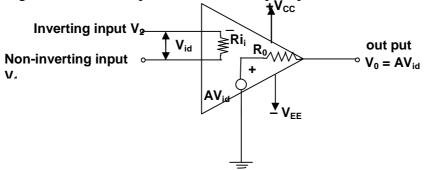

Figure 4.1 Schematic Diagram of a Differential Amplifier

For a linear active device with two input signals v1 and v2 and the output signals v0 each measured with respect to ground, we have

$$v_0 = A(v_1 - v_2)$$

------ (4.1)

where A is the voltage gain of the differential amplifier. In actual practice, the output depends not only upon the difference of the two input signals but also upon the average level. In symmetrical circuits we talk about the in-phase signals (called common mode (CM) Signals  $v_c$ ) and the difference or anti-phase signals (called differential mode (DM) signals  $v_d$ ). They are defined as

$$v_c = \frac{1}{2}(v_1+v_2)$$

, and  $vd = (v_1 - v_2)$  ------ (4.2)

The output  $v_0$  can be expressed as linear combination of the two input voltages, as

$$v_0 = A_1 v_1 + A_2 v_2$$

------ (4.3)

Where  $A_1$  and  $A_2$  are the voltage amplifications from input 1 and 2 respectively. From equations (4.2)

and (4.3) we get

$$v_{o} = A_{1}(v_{c} + \frac{1}{2}v_{d}) + A_{2}(v_{c} - \frac{1}{2}v_{d}) = (A_{1} + A_{2})v_{c} + \frac{1}{2}(A_{1} - A_{2})v_{d} = A_{c}v_{c} + A_{d}v_{d}$$

-----(4.4)

where  $A_c = A_1 + A_2$  and  $A_d = \frac{1}{2}(A_1 - A_2)$ , are voltage gains for the signals in common mode and differential modes respectively. They may be defined as

$$\mathbf{A}_{d} = \left(\frac{\mathbf{v}_{0}}{\mathbf{v}_{d}}\right)_{\mathbf{v}_{c}=0} \text{ and } \mathbf{A}_{c} = \left(\frac{\mathbf{v}_{0}}{\mathbf{v}_{c}}\right)_{\mathbf{v}_{d}=0}$$

-----(4.5)

Thus,  $A_d$  can be measured directly by setting  $v_c = 0$ , or  $v_2 = -v_1$ .

The  $A_c$  can be measured by setting  $v_d = 0$ , or  $v_2 = v_1$ , generally the desired signals in differential amplifier are DM and undesired signals are CM. The figure of merit for differential amplifiers in defined as

$$\rho = \left[\frac{A_d}{A_c}\right] \tag{4.6}$$

4.3

This is called the common-mode rejection ratio (CMRR) and is also sometimes referred to as the discrimination factor of a differential amplifier. Ideally  $A_c=0$ , and CMRR=  $\infty$ . In practice, A/c is non-zero but very small, whereas  $A_d$  is very large. The combination of equations (4.4) and (4.6) gives

$$Vo = A_{d}v_{d} \left[ 1 + \frac{A_{c} v_{c}}{A_{d} v_{d}} \right] = A_{d}v_{d} \left[ 1 + \frac{v_{c}}{v_{d}} \cdot \frac{1}{CMRR} \right]$$

$$V_{0} = A_{d}v_{d} \text{ (since CMRR = $\infty$)} \qquad ------(4.7)$$

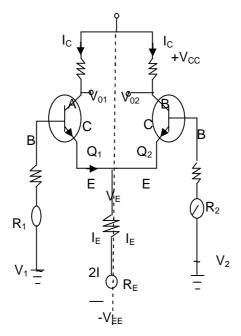

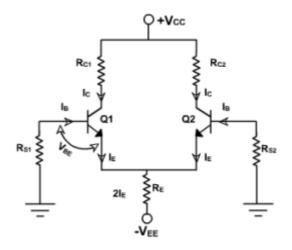

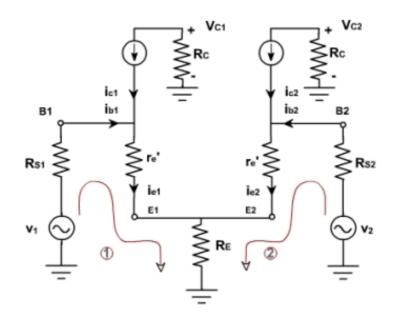

A basic differential amplifier circuit (ckt), consisting of two interlocked common emitter amplifier stages is shown in figure 4.2. The two stages are linked by having both emitters connected to a constant current generator. As current through one emitter increases, current through the other decreases.

The circuit is symmetrical about the vertical dashed line and the two transistors and resistors  $R_c$  form a bridge circuit that is balanced under zero input signal. The resistors and the transistors are simultaneously fabricated in adjacent areas on a small chip. They will be at the same temperature. A simultaneous change in  $h_{FE}$  or  $v_{BE}$  will produce equal changes in the voltages at a and b and  $v_0$  will not be affected.

Figure 4.2 Basic Differential Amplifier Circuit Diagram

Consider the circuit operation with no input signals. For  $v_1=v_2=0$ , an emitter current  $I_E$  flows in each BJT. Therefore  $I_C = I_E$  and

$$V_{01} = V_{02} = V_{CC} - I_C R_C ------(4.8)$$

thus the base current  $I_B = \frac{I_E}{h_{FE}}$  ------(4.9)

and  $V_E = -I_B R_1 - V_{BE}$  ------(4.10)

If  $v_{\text{CE}}$  is chosen large enough to bias each BJT in the center or the linear operating region, then

4.4

$$V_{CC} = V_{EE} + 2 I_E R_E + V_{CE} + I_C R_C$$

------(4.11)

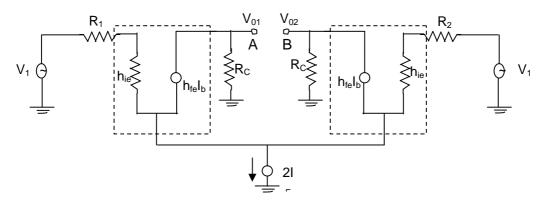

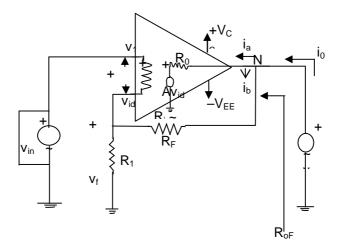

The ac equivalent circuit for use differential amplifier is shown in fig (4.3). Here it is assumed

$h_{oe} R_C \ll 1$  or  $h_{oe} \ll 1/R_C$  and thus  $h_{oe}$  is omitted in this figure. The collector current  $I_c = h_{fe}$ Ib. The voltage  $h_{re}v_c$  is neglected in comparison with the  $h_{ib}I_b$  drop across  $h_{ie}$

Figure 4.3 AC Equivalent Circuit of Basic Differential Amplifier

#### 4.1.1 Common Mode Voltage Gain:

Let

$$v_1 = v_2 = v_s$$

, user  $A_c = \frac{v_o}{v_c} = \frac{v_o}{v_s}$

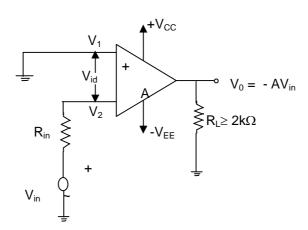

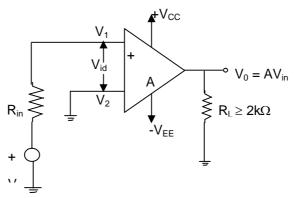

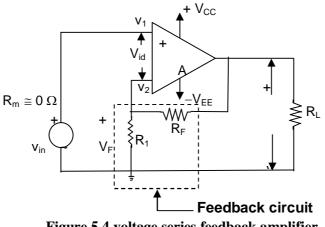

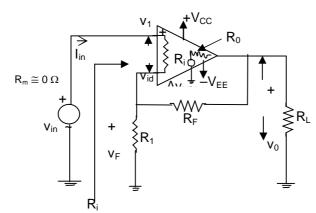

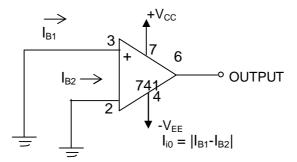

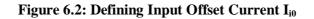

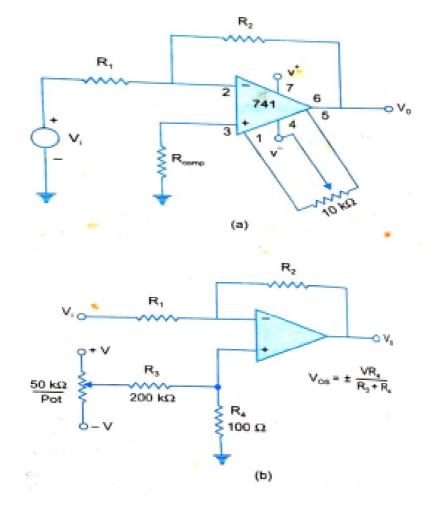

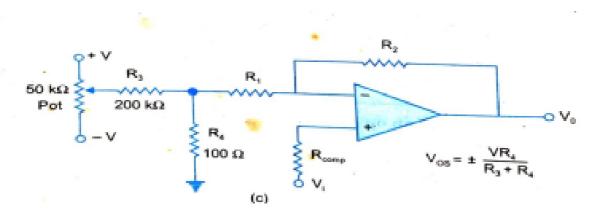

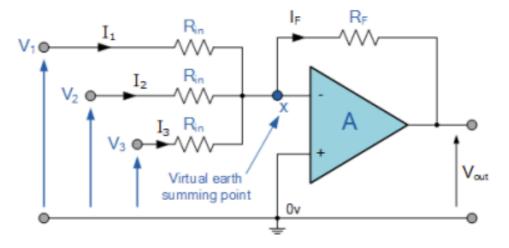

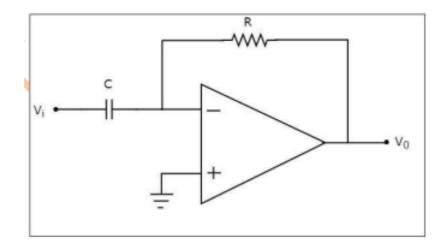

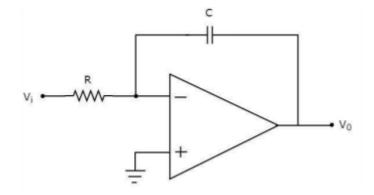

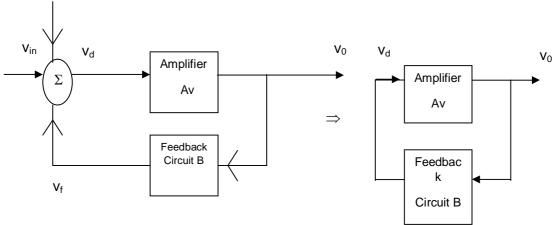

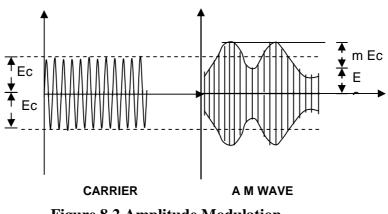

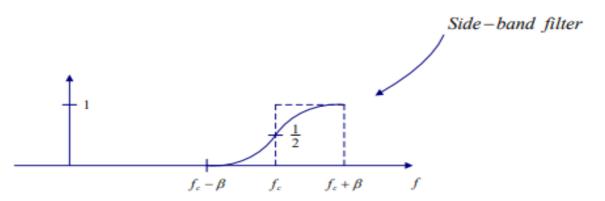

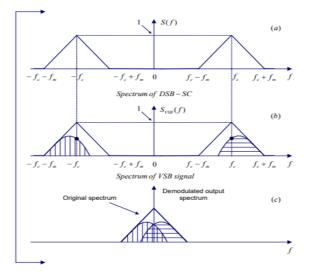

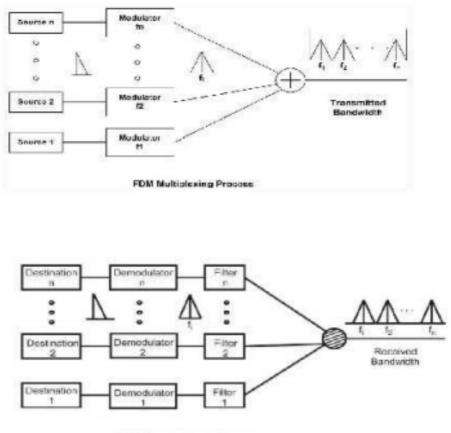

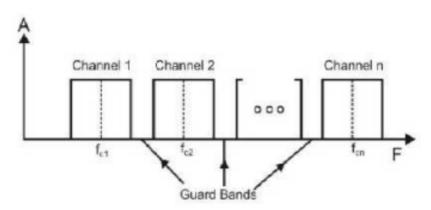

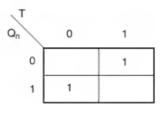

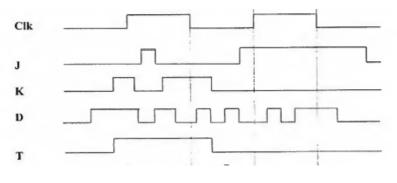

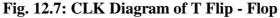

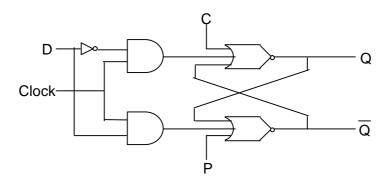

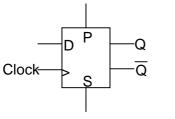

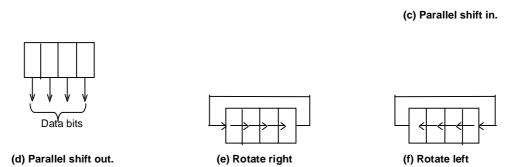

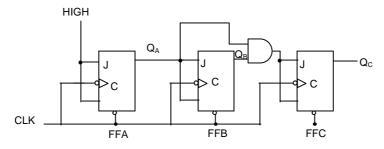

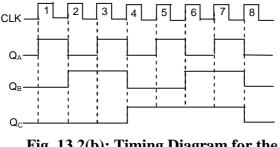

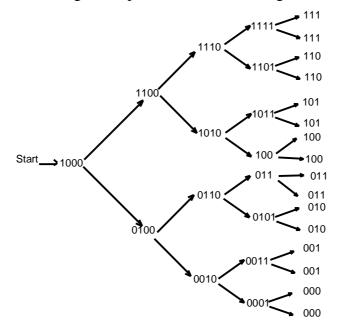

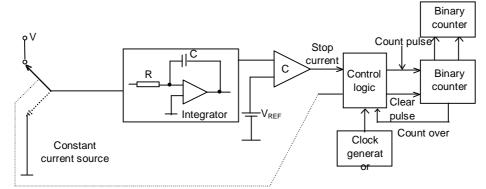

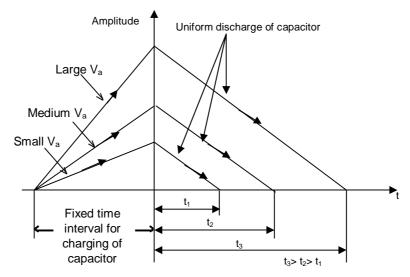

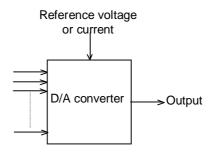

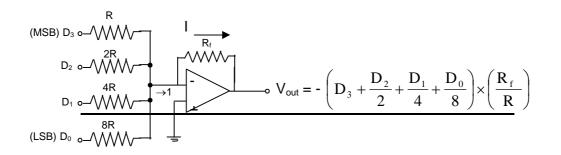

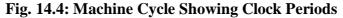

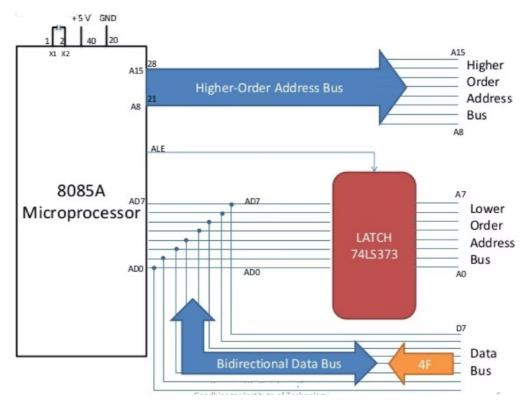

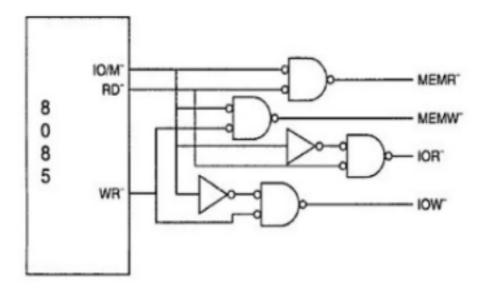

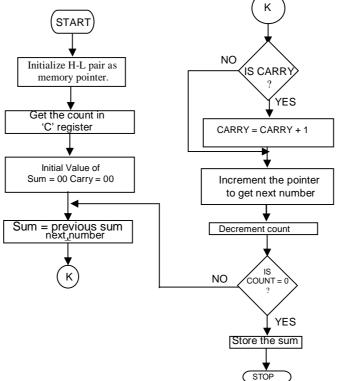

Due to symmetry, each input at the base, sees a common emitter circuit, with an un bypassed emitter resister of  $2R_E$  (The emitter resistor is effectively doubled, as it carries the emitter current for both transistors). Thus we have